73

Chapter 3 MB91460 Series Basic Information

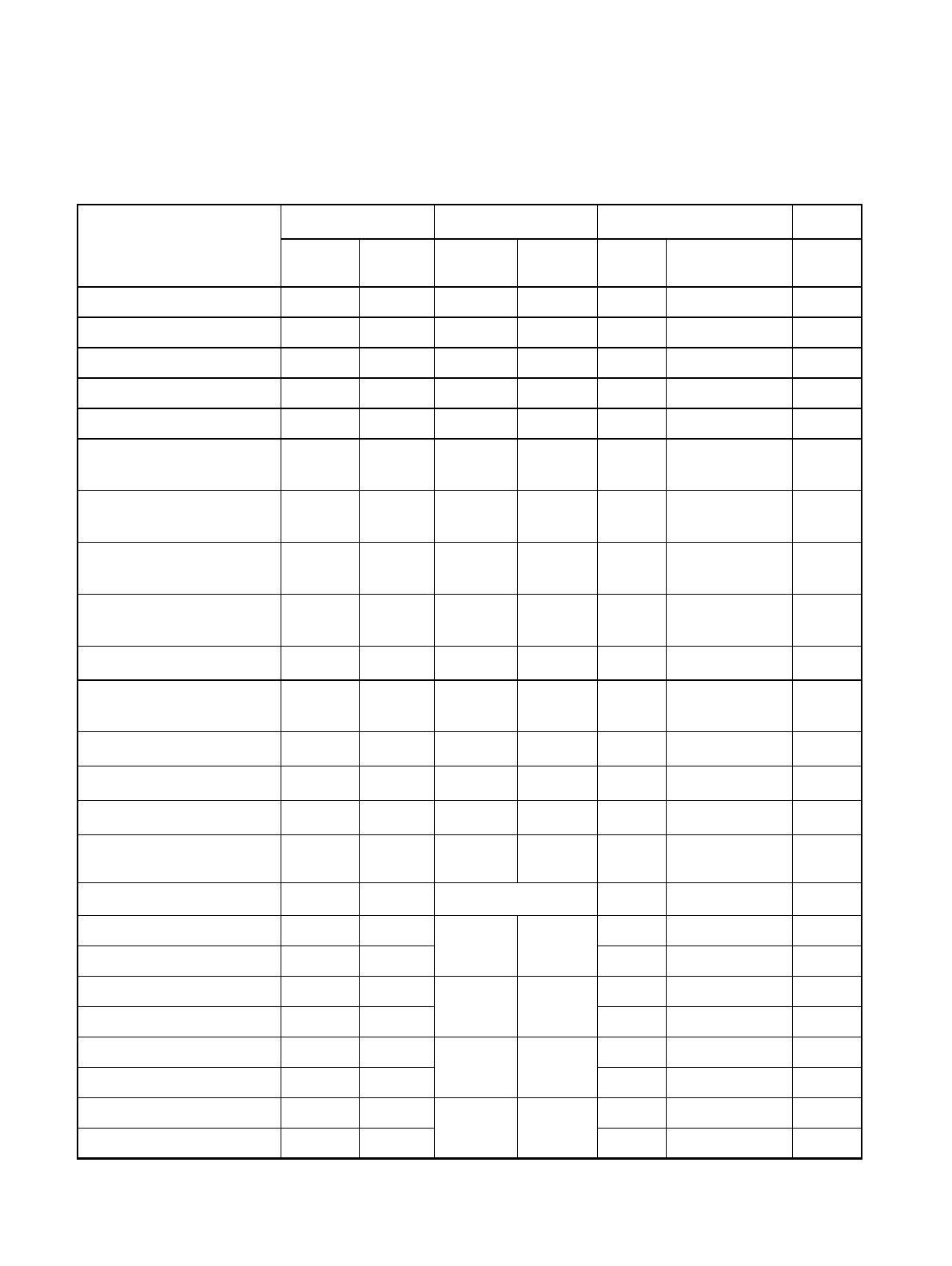

3.Interrupt Vector Table

3. Interrupt Vector Table

This section shows the allocation of interrupt and interrupt vector/interrupt register.

Interrupt

Interrupt number

Interrupt level

*1

Interrupt vector

*2

Decimal

Hexa-

decimal

Setting

Register

Register

address

Offset

Default Vector

address

RN

*8

Reset 0 00 - - 0x3FC 0x000FFFFC

Mode vector 1 01 - - 0x3F8 0x000FFFF8

System reserved 2 02 - - 0x3F4 0x000FFFF4

System reserved 3 03 - - 0x3F0 0x000FFFF0

System reserved 4 04 - - 0x3EC 0x000FFFEC

CPU supervisor mode

(INT #5 instruction)

*6

5 05 - - 0x3E8 0x000FFFE8

Memory Protection excep-

tion

*6

6 06 - - 0x3E4 0x000FFFE4

Co-processor

fault trap

*5

7 07 - - 0x3E0 0x000FFFE0

Co-processor

error trap

*5

8 08 - - 0x3DC 0x000FFFDC

INTE instruction

*5

9 09 - - 0x3D8 0x000FFFD8

Instruction break

exception

*5

10 0A - - 0x3D4 0x000FFFD4

Operand break trap

*5

11 0B - - 0x3D0 0x000FFFD0

Step trace trap

*5

12 0C - - 0x3CC 0x000FFFCC

NMI interrupt (tool)

*5

13 0D - - 0x3C8 0x000FFFC8

Undefined instruction

exception

14 0E - - 0x3C4 0x000FFFC4

NMI request 15 0F

F

H

fixed

0x3C0 0x000FFFC0

External Interrupt 0 16 10

ICR00 0x440

0x3BC 0x000FFFBC 0, 16

External Interrupt 1 17 11 0x3B8 0x000FFFB8 1, 17

External Interrupt 2 18 12

ICR01 0x441

0x3B4 0x000FFFB4 2, 18

External Interrupt 3 19 13 0x3B0 0x000FFFB0 3, 19

External Interrupt 4 20 14

ICR02 0x442

0x3AC 0x000FFFAC 20

External Interrupt 5 21 15 0x3A8 0x000FFFA8 21

External Interrupt 6 22 16

ICR03 0x443

0x3A4 0x000FFFA4 22

External Interrupt 7 23 17 0x3A0 0x000FFFA0 23