540

Chapter 31 External Bus

2.External Bus Interface Registers

[Bits 22 - 20] RFC2, RFC1, RFC0 (ReFresh Count): Refresh count

Set these bits to the number of times a refresh must be performed to refresh all SDRAM.

Table 4.2-45 shows the number of times to refresh.

The number of times to refresh specified here is the number of times centralized refreshing is performed before

and after transition to the self - refresh mode. When burst refreshing has been selected with the BRST bit, the

number of times to refresh is also the number of times the refresh command is issued at every refresh interval.

[Bit 19] PON (Power ON): Power - on control

This bit is used to control the SDRAM (FCRAM) power - on sequence.

Table 4.2-46 shows the function of power - on control.

Writing 1 to the PON bit starts the SDRAM power - on sequence.

Before starting the power - on sequence, be sure to set the relevant registers such as AWR, MCRA(B), and

CSER.

This bit returns to 0 as soon as the power - on sequence is started.

When enabling the PON bit, set RFINT and enable RRLD to activate the refresh counter.

Refreshing is not performed only with the PON bit.

Do not enable this bit along with the SELF bit.

When read by a Read - modify - Write instruction, the bit always returns 0.

[Bits 18 - 16] TRC2, TRC1, TRC0 (Time of Refresh Cycle): Refresh cycle (tRC)

These bits set the refresh cycle (tRC).

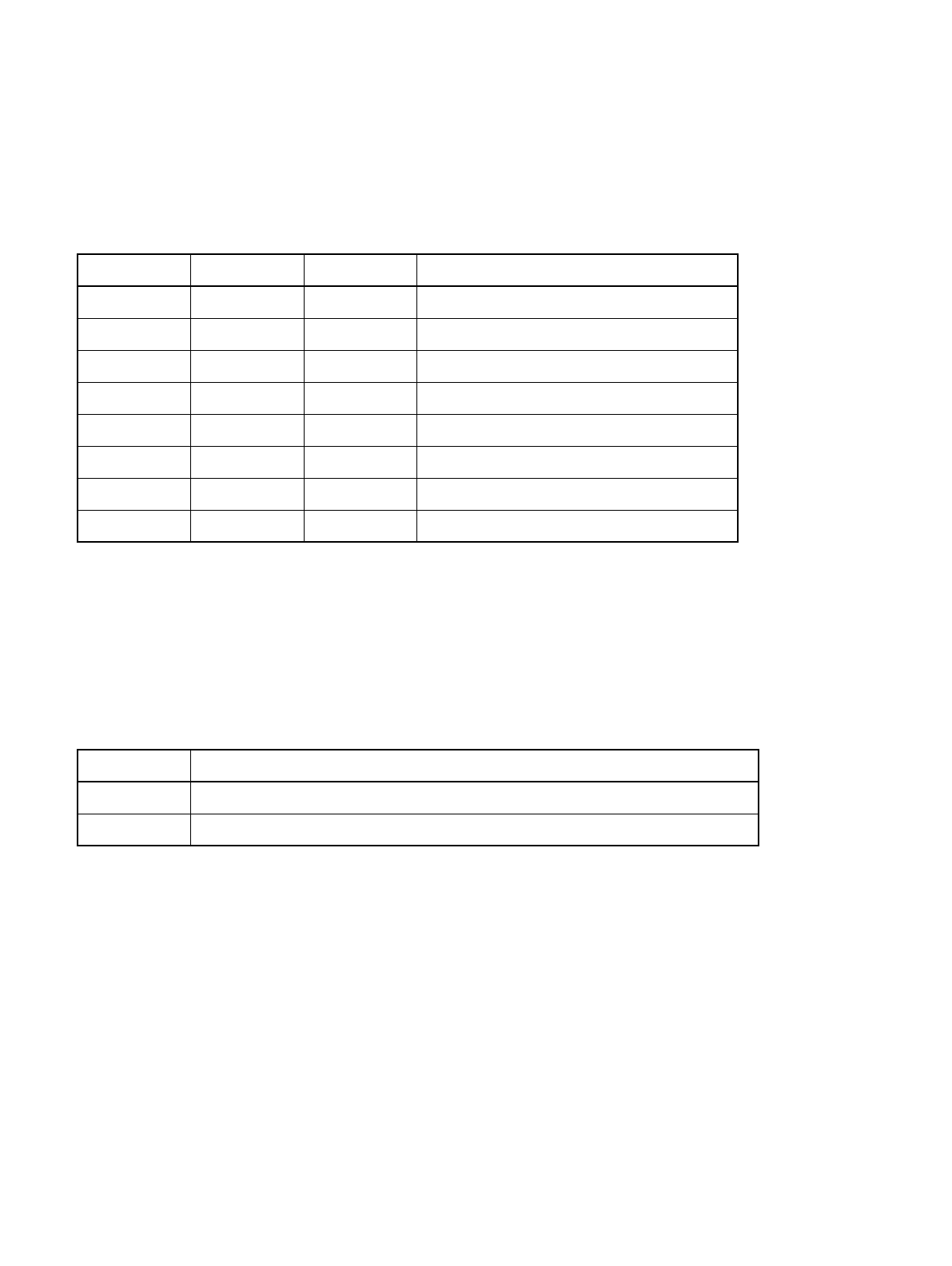

Table 2-29 Number of times to refresh

RFC2 RFC1 RFC0 Number of times to refresh

000256

001512

0 1 0 1024

0 1 1 2048

1 0 0 4096

1 0 1 8192

1 1 0 Setting prohibited

1 1 1 Refresh prohibited

Table 2-30 Function of power - on control

PON Power-on control

0 Disabled (no-operation)

1 Start power-on sequence