526

Chapter 31 External Bus

2.External Bus Interface Registers

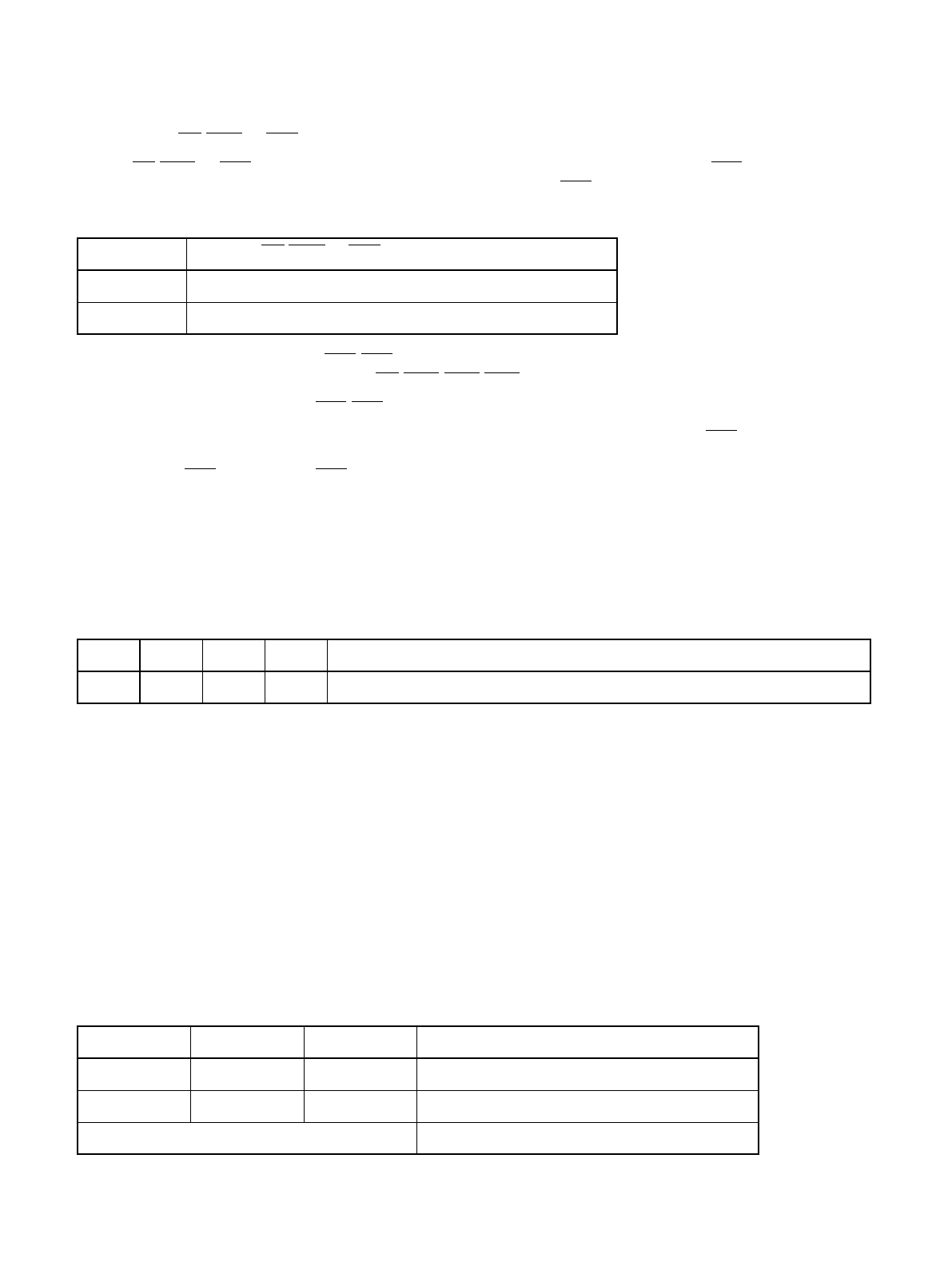

[Bits 0] W00 (RD/WRn -> CSn Hold Extension Cycle)

The RD/WRn -> CSn hold extension cycle is set to extend the period before negating CSn after the read/write

strobe is negated. One hold extension cycle is inserted before CSn is negated after the read/write strobe is

negated.

If 0 cycle is selected by setting 0, CS0-CS7 are negated after the hold delay after it starts on the rising edge of

external memory clock MCLK output after RD/WR0-WR3/WRn are negated.

If 1 cycle is selected by setting 1, CS0-CS7 are negated one cycle later.

When making successive accesses within the same chip select area without negating CSn, the hold extension

cycle is not inserted. If a hold extension cycle for determining the address is required, set the W02 bit and insert

the address -> CSn delay. Since CSn is negated for each access operation, this hold extension cycle is enabled.

● Memory type A(SDRAM/FCRAM) and Memory type B(FCRAM)

The chip select areas for which the access type (TYP3 to TYP0 bits) in the ACR6 and ACR7 registers has been

set as in Table 1.2 - 18 serve for SDRAM/FCRAM access.

Table 1.2 - 18 lists the access type settings (TYP3 to TYP0 bits).

The following explains those functions of individual bits in AWR6 and AWR7 which apply to SDRAM access

areas. As the initial value is undefined, set the access type before each area is enabled by the chip select area

enable register (CSER).

For all the areas connected to SDRAM/FCRAM, use the same settings for this type of registers.

The following summarizes the functions of individual bits in the area wait registers (AWR6 and AWR7).

[Bit 15] W15: Reserved bit

Be sure to set this bit to 0.

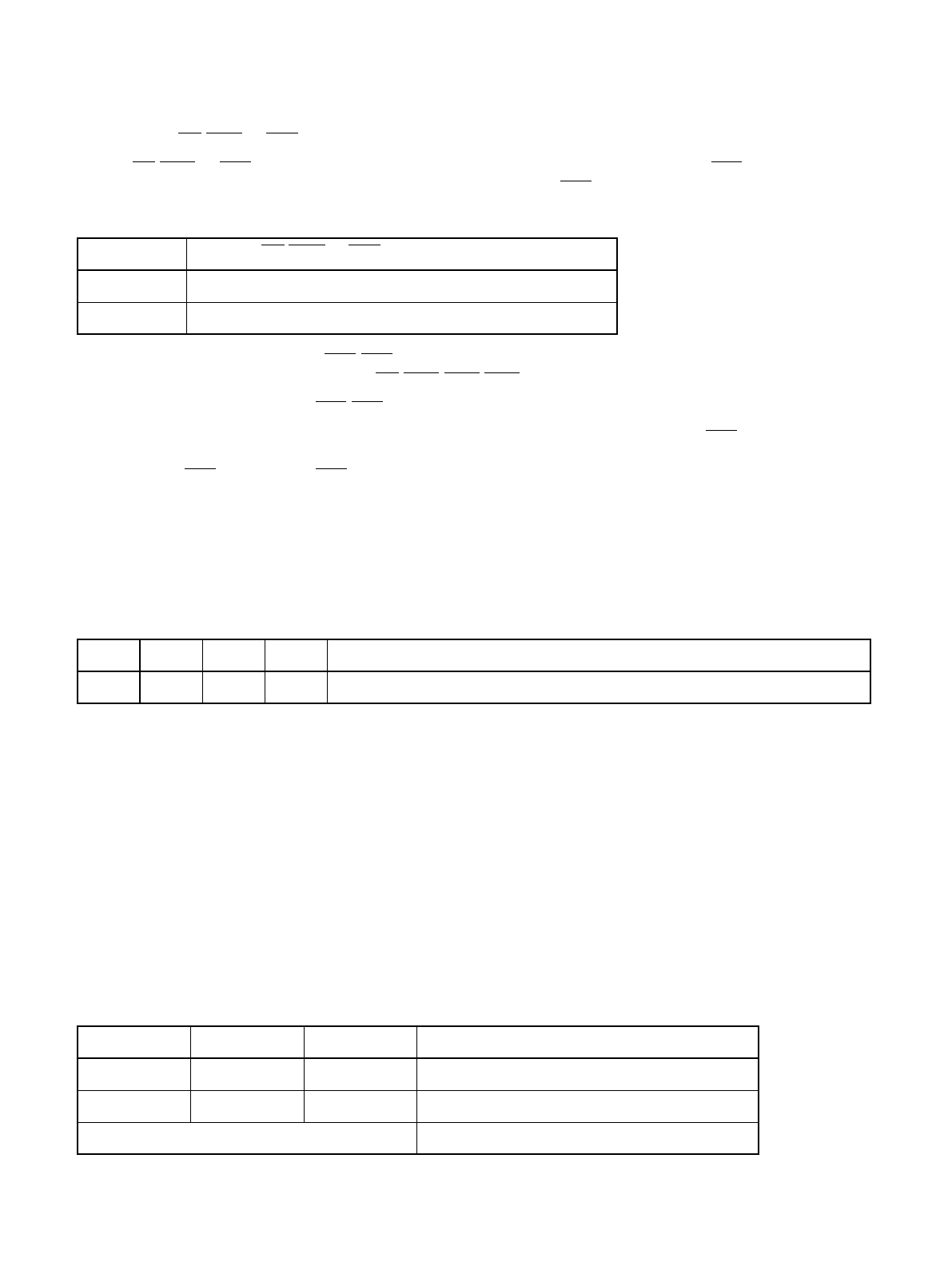

[Bits 14 - 12] W14 to W12 (RAS - CAS delay Cycle): RAS - CAS delay cycles

Set these bits to the number of cycles from RAS output to CAS output.

Table 4.2 - 19 lists the settings for the number of cycles from RAS output to CAS output.

W00 RD/WRn -> CSn hold extension cycle

0 0 cycle

1 1 cycle

Table 2-9 Access Type Settings (TYP3 - TYP0 Bits)

TYP3 TYP2 TYP1 TYP0 Access type

1 0 0 0 Memory type A: SDRAM/FCRAM (Auto - precharge is not used.)

Table 2-10 Setting the Number of Cycles from RAS Output to CAS Output

W14 W13 W12 RAS-CAS delay cycle

0 0 0 1 cycle

0 0 0 2 cycles

... ...