584

Chapter 31 External Bus

9.SDRAM/FCRAM Interface Operation

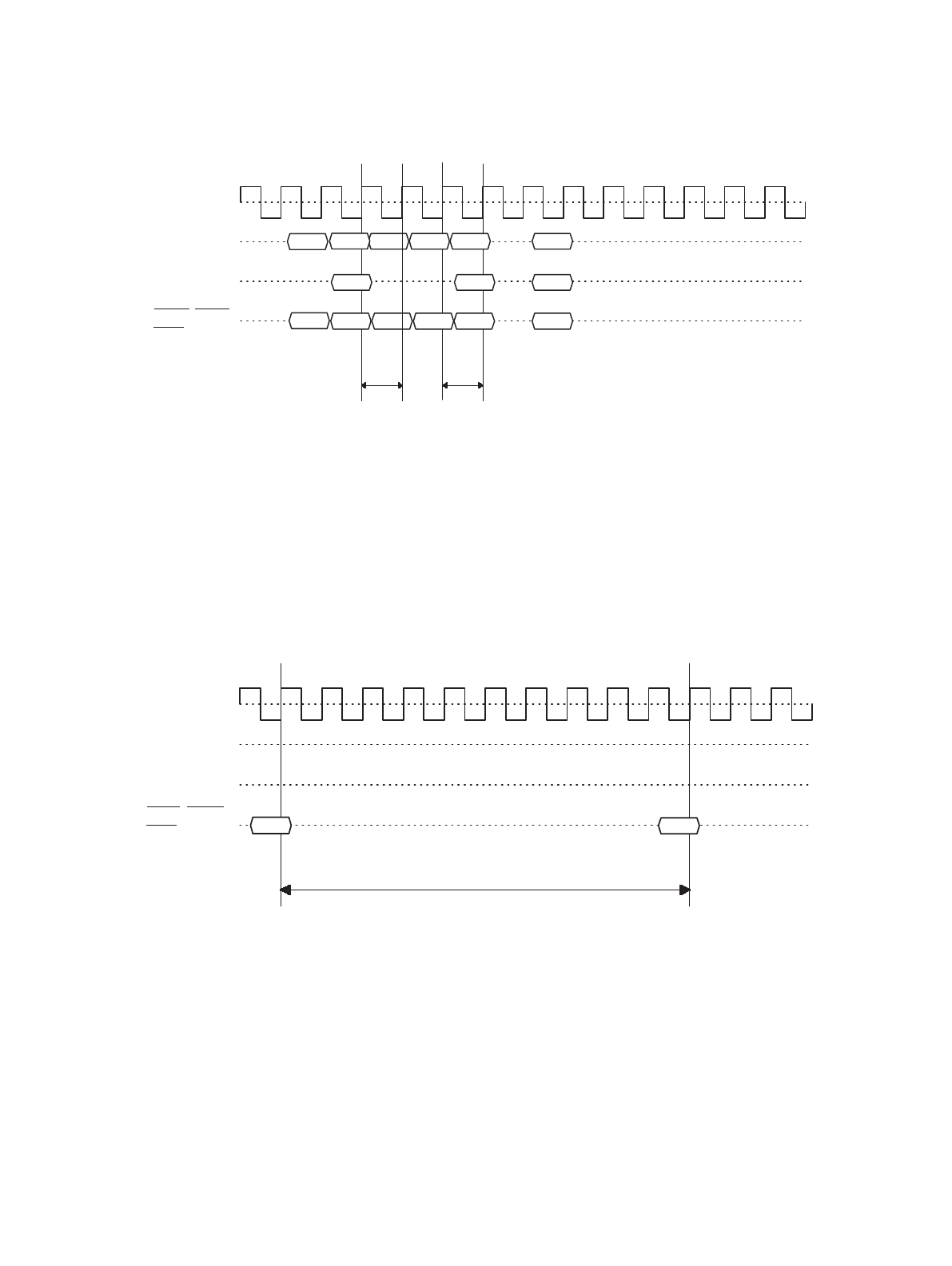

Figure 9-4 Single Read/Write Timing Chart

• Setting TYP to 1001

B

causes a read/write command with auto - precharge to be issued. Since the cycle from

READA/WRITA issuance to ACTV issuance is fixed at CL + BL - 1, however, TYP can be set to 1001

B

only

when FCRAM is connected.

• This timing is effective, for example, for recurring page misses as it eliminates the cycle for issuing the PRE

command.

■ Auto - refresh Operation Timing

Figure 9-5 shows auto - refresh operation timings.

Figure 9-5 Auto - refresh Timing Chart

• The refresh command is issued every " refresh control register's (RCR's) RFINT5 - RFINT0 value x 32 " cycles

and access is restarted upon completion of each refresh.

• Set the TRC bit in the refresh control register (RCR) according to the SDRAM/FCRAM standards.

• Satisfy the maximum RAS active time as well.

9.1 Self Refresh

This section describes self - refreshing.

MCLK

A

D

Row Col

ACTV READAACTV

Row

Col

WRITA

#1

#2

Row

ACTV WRITA

Col

#3

CL+BL-1CL+BL-1

SRAS,SCAS,

SWE

MCLK

A

D

REF

tRC

Refresh cycle

ACTV

SRAS,SCAS,

SWE