836

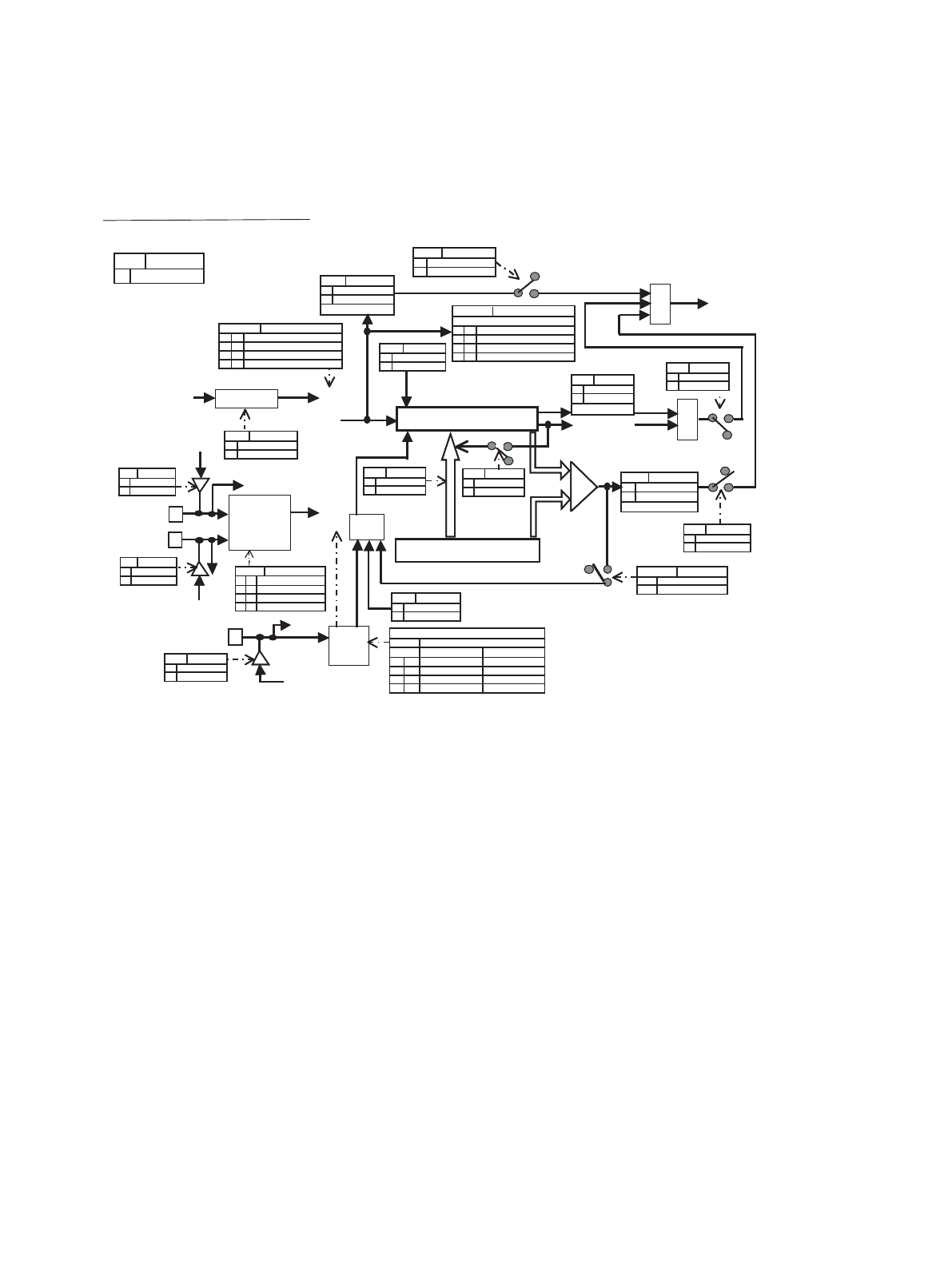

Chapter 41 Up/Down Counter

3.Configuration

3. Configuration

Figure 3-1 Configuration Diagram

UDCR0

UDRC0

CITE

UDCS0: bit6

0

1

CMS1-0 UDCC0: bit11-10

0

0

1

10

11

0

CES1-0 UDCC0: bit 9-8

0

0

1

10

11

0

UDCC0: bit1-0, bit 2

CGE1-0

0

0

1

10

11

0

CGS C

UDCLR UDCC0: bit2

0

1

Clear

Disabling

UDIE

UDCS0: bit5

1

0

UDFF

UDCS0: bit2

0

1

CSTR

UDCS0: bit7

0

1

Start counting

CFIE

UDCC0: bit 13

0

1

CLKS

UDCC0: bit 12

0

1

OR

OR

1

1

1

0

0

1

0

0

UDF1-0 UDCS0: bit 1-0

0

0

1

10

11

0

M16E UDCC0: bit15

0

8 bit mode

Up/Down Counter 0 (8 Bit Mode)

AIN0/SIN2/P20.0

P20EPFR20.0

0

1

BIN0/SOT2/P20.1

P20 EPFR20.1

0

1

ZIN0/SCK2/P20.2

P20 EPFR20.2

0

1

OR

UCRE UDCC0:bit5

0

1

CTUT

UDCC0: bit6

0

1

1

0

RLDE UDCC0: bit4

0

1

CDCF

UDCC0: bit14

0

1

CMPF

UDCS0: bit4

0

1

OVFF

UDCS0: bit3

0

1

--

0

0

1

10

11

0

00

00

0

0

1

--

0

0

0

0

0

0

0

Timer mode (Countdown only)

Up/down count mode

Phase difference count mode (Multiply by 2)

Phase difference count mode (Multiply by 4)

No change direction

Direction changed

Stop counting

Disable interrupts

Enable interrupts

8 bit mode

WRITE 0: Flag clear

Peripheral clock

CLKP

Prescaler

CLKP divided by 2

CLKP divided by 8

From port data

register

From port data

register

From port data

register

Others

Enable UDC

Others

Enable UDC

Others

Enable UDC

Read from port

Read

from

port

Read from

port

Edge

detection

Edge

detection

Disable edge detection

Enable falling edge detection

Enable rising edge detection

Enable both edge detection

Gate

Activation

No impact

Data transfer

* Only 16 bit transfer is enabled

while counting stops.

Up/Down Counter (Read only)

Reload/compare register (Write only)

Reload

Counter clear

Disable reload

Enable reload

No input

Countdown

Countup

Both countdown and countup

Write: Disabled, Read only

Selector/Count Control

Disable edge detection

Enable falling edge detection

Enable rising edge detection

Disable setting

Disable level detection

Enable LOW level detection

Enable HIGH level detection

Disable setting

1: Gate function

0: Counter clear function

Com-

pare

UDC0 interrupt

(#128)

Compare match

No compare match

Disable interrupts

Enable interrupts

Disable interrupts

Enable interrupts

No underflow

Underflowed

Disable counter clear

Enable counter clear

No overflow

Overflowed

WRITE 0: Flag clear

WRITE 0: Flag clear

WRITE 0: Flag clear