143

Chapter 9 Reset

4.Registers

4.2 STCR: Standby Control Register

This register is used for software reset control (changing to standby mode, pin control in stop mode, and clock

oscillation halted in stop mode), and specifies the oscillation stabilization wait time.

Note: See also “Chapter 10 Standby (Page No.155)”.

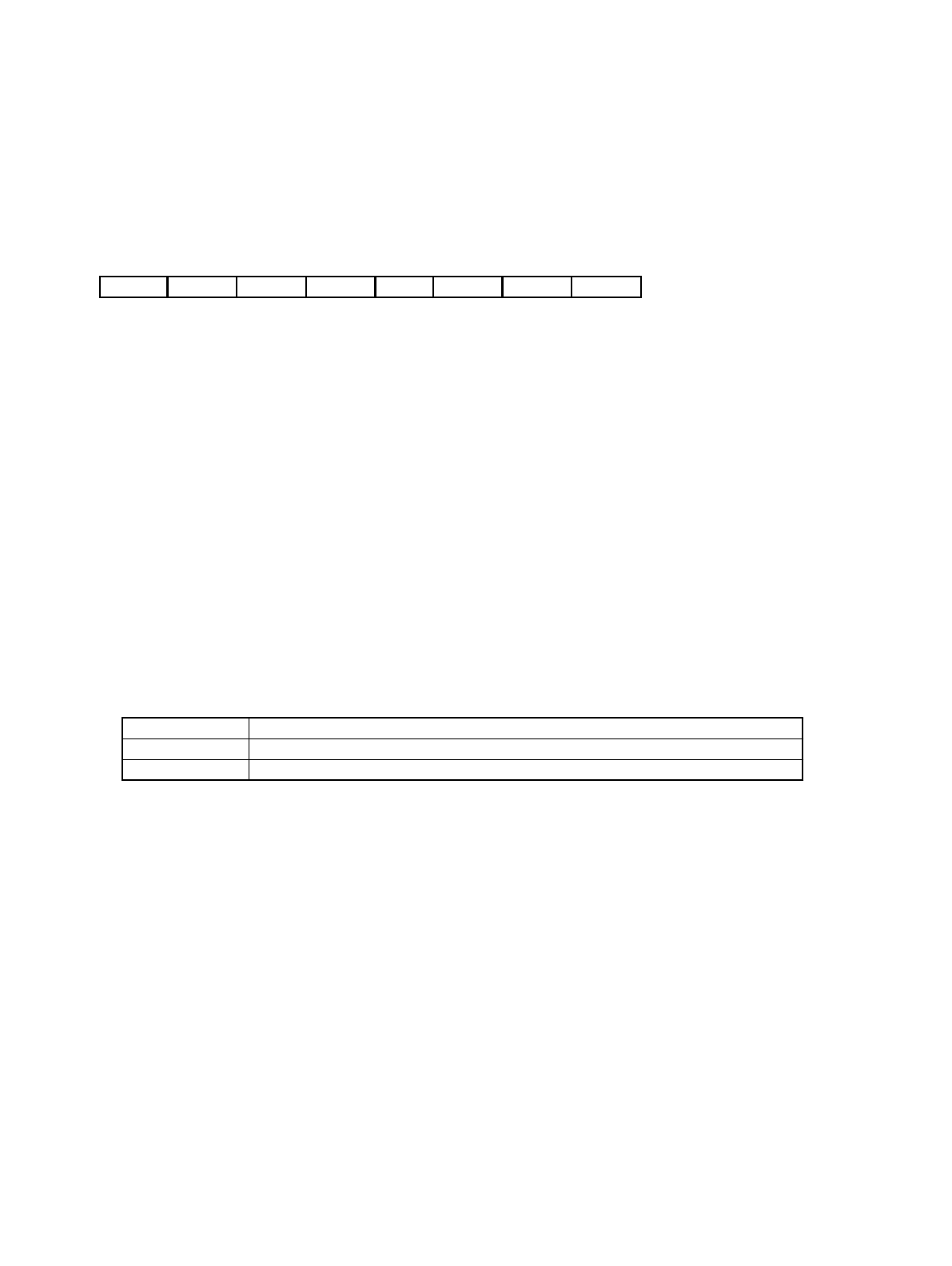

• STCR: Address 0481h (Access: Byte, Half-word)

Note: See “Meaning of Bit Attribute Symbols (Page No.10)” for details of the attributes.

• Bit7: Stop mode

Writing “1” to the stop mode bit (STOP) changes to stop mode.

See “Chapter 10 Standby (Page No.155)” for details.

• Bit6: Sleep mode

Writing “1” to the sleep mode bit (SLEEP) changes to sleep mode.

See

“Chapter 10 Standby (Page No.155)” for details.

• Bit5: High impedance mode

Writing “1” to the high impedance mode bit (HIZ) sets pin to high impedance (Hi-z) during stop mode.

See

“Chapter 10 Standby (Page No.155)” for details.

• Bit4: Software reset

Writing “0” to the software reset bit triggers a software reset.

• Note that negative logic is used.

• The read value is always “1”.

• Bit3-2: Oscillation stabilization time selection

The oscillation stabilization time selection bits (OS[1:0]) set the oscillation stabilization time as follows:

(F2 x 2

1

, F2 x 2

11

, F2 x 2

16

, F2 x 2

22

)

The count is supplied by the timebase counter.

Initialized to “00” (F2 x 2

1

, main clock) by a reset triggered by INIT pin input.

See “Chapter 19 Timebase Timer (Page No.263)” for details.

• Bit1: Halt sub clock oscillation

Writing “1” to the halt sub clock oscillation bit (OSCD2) halts the oscillation of the sub clock during stop mode.

• Bit0: Halt main clock oscillation

Writing “1” to the halt main clock oscillation bit (OSCD1) halts the oscillation of the main clock during stop mode.

76543210 bit

STOP SLEEP HIZ SRST OS1 OS0 OSCD2 OSCD1

00110011

Initial value

(INIT pin input)

0011XX11

Initial value

(Watchdog reset)

00X1XXXX

Initial value

(Software reset)

R/W R/W R/W R1,W R/W R/W RX/WX R/W Attribute

SRST Operation

0 Trigger a software reset

1 Do not trigger a software reset