768

Chapter 37 Output Compare

7.Q & A

7. Q & A

7.1 How do I set the compare value?

Write the compare value to compare registers OCCP0 - OCCP7.

7.2 How do I set the compare mode? (for OCU1, OCU3, OCU5, OCU7 output)

This is done using compare mode bits (OCS01.CMOD), (OCS23.CMOD), (OCS45.CMOD), (OCS67.CMOD).

With no relation to CMOD bit,

OCU0 output is reversed by a compare-match between free-run timer 2 and compare register 0 only.

OCU2 output is reversed by a compare-match between free-run timer 3 and compare register 2 only.

OCU4 output is reversed by a compare-match between free-run timer 6 and compare register 4 only.

OCU6 output is reversed by a compare-match between free-run timer 7 and compare register 6 only.

7.3 How do I enable/disable the compare operation?

Set it via the compare operation permission bit (OCS01.CST[1:0]), (OCS23.CST[1:0]), (OCS45.CST[1:0]),

(OCS67.CST[1:0]).

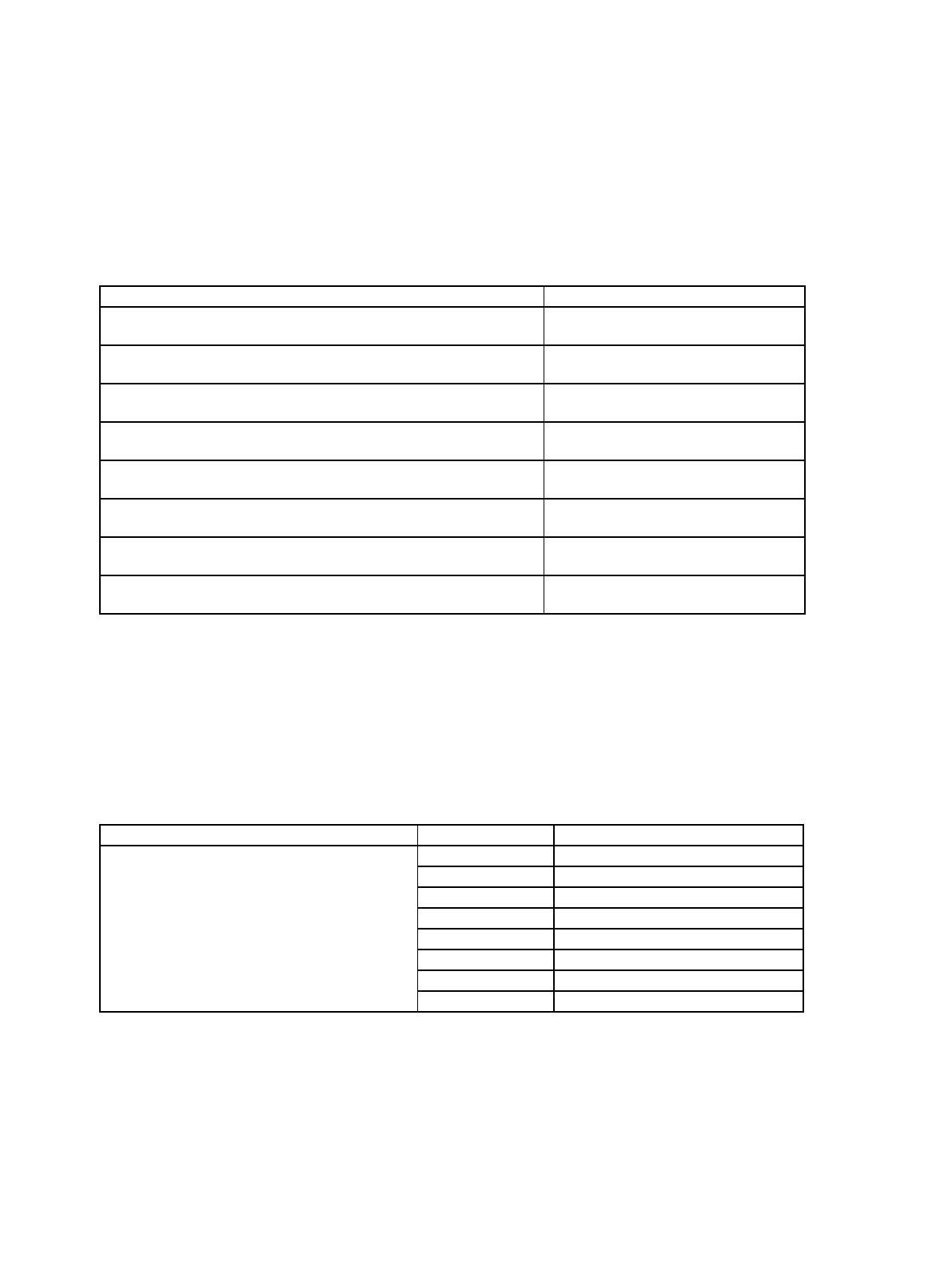

Operation Compare mode bit

To reverse OCU1 output using a compare-match from only free-run timer 2

and compare register 1

Set (OCS01.CMOD) bit to “0”

To reverse OCU3 output using a compare-match from only free-run timer 3

and compare register 3

Set (OCS23.CMOD) bit to “0”

To reverse OCU5 output using a compare-match from only free-run timer 6

and compare register 5

Set (OCS45.CMOD) bit to “0”

To reverse OCU7 output using a compare-match from only free-run timer 7

and compare register 7

Set (OCS67.CMOD) bit to “0”

To reverse OCU1 output using a compare-match from free-run timer 2 and

compare register 0, as well as free-run timer 0 and compare register 1

Set (OCS01.CMOD) bit to “1”

To reverse OCU3 output using a compare-match from free-run timer 3 and

compare register 2, as well as free-run timer 1 and compare register 3

Set (OCS23.CMOD) bit to “1”

To reverse OCU5 output using a compare-match from free-run timer 6 and

compare register 4, as well as free-run timer 4 and compare register 1

Set (OCS45.CMOD) bit to “1”

To reverse OCU7 output using a compare-match from free-run timer 7 and

compare register 6, as well as free-run timer 5 and compare register 3

Set (OCS67.CMOD) bit to “1”

Operation Compare Compare operation permission bit

To stop (disable) the compare operation

Compare 0 Set (OCS01.CST[0]) to “0”

Compare 1 Set (OCS01.CST[1]) to “0”

Compare 2 Set (OCS23.CST[0]) to “0”

Compare 3 Set (OCS23.CST[1]) to “0”

Compare 4 Set (OCS45.CST[0]) to “0”

Compare 5 Set (OCS45.CST[1]) to “0”

Compare 6 Set (OCS67.CST[0]) to “0”

Compare 7 Set (OCS67.CST[1]) to “0”