606

Chapter 31 External Bus

10.DMA Access Operation

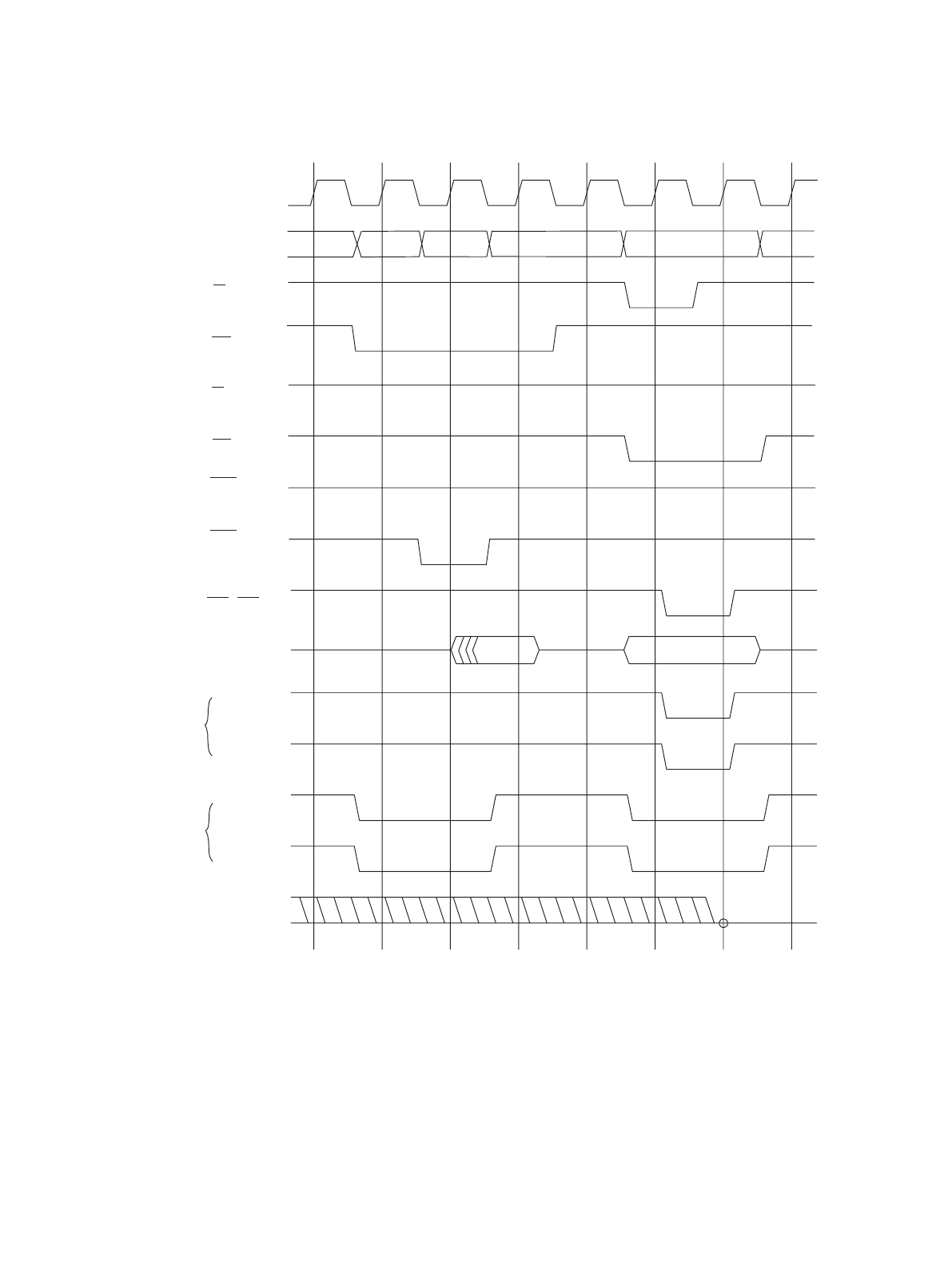

Figure 10-12 Timing Chart for Two - cycle Transfer (SDRAM/FCRAM to I/O)

MCLK

A31 to 0

AS

CSn

RD

CSn

memory

address

I/O address

WRn(SWE)

D31 to 0

DACKn

DEOPn

DACKn

DEOPn

DREQn

FR30

compatible

mode

Basic

mode

SRAS

SCAS