756

Chapter 36 Input Capture

7.Q&A

Interrupt request flags (ICS01.ICP0), (ICS01.ICP1), (ICS23.ICP0), (ICS23.ICP1), (ICS45.ICP0), (ICS45.ICP1),

(ICS67.ICP0), (ICS67.ICP1) are not automatically cleared, so please set the input capture interrupt request

flag (ICP1, ICP0) to “0” to clear them before returning from interrupt processing.

7.4 What are the types of interrupts?

There is only one kind of interrupt, and it is generated by input signal edge detection.

7.5 How do I enable interrupts?

Interrupt request permission, interrupt request flag

Interrupts are enabled via interrupt request permission bit (ICS01.ICE0), (ICS01.ICE1), (ICS23.ICE0),

(ICS23.ICE1), (ICS45.ICE0), (ICS45.ICE1), (ICS67.ICE0), (ICS67.ICE1).

Clearing of interrupt requests is done using interrupt request bit (ICS01.ICP0), (ICS01.ICP1), (ICS23.ICP0),

(ICS23.ICP1), (ICS45.ICP0), (ICS45.ICP1), (ICS67.ICP0), (ICS67.ICP1).

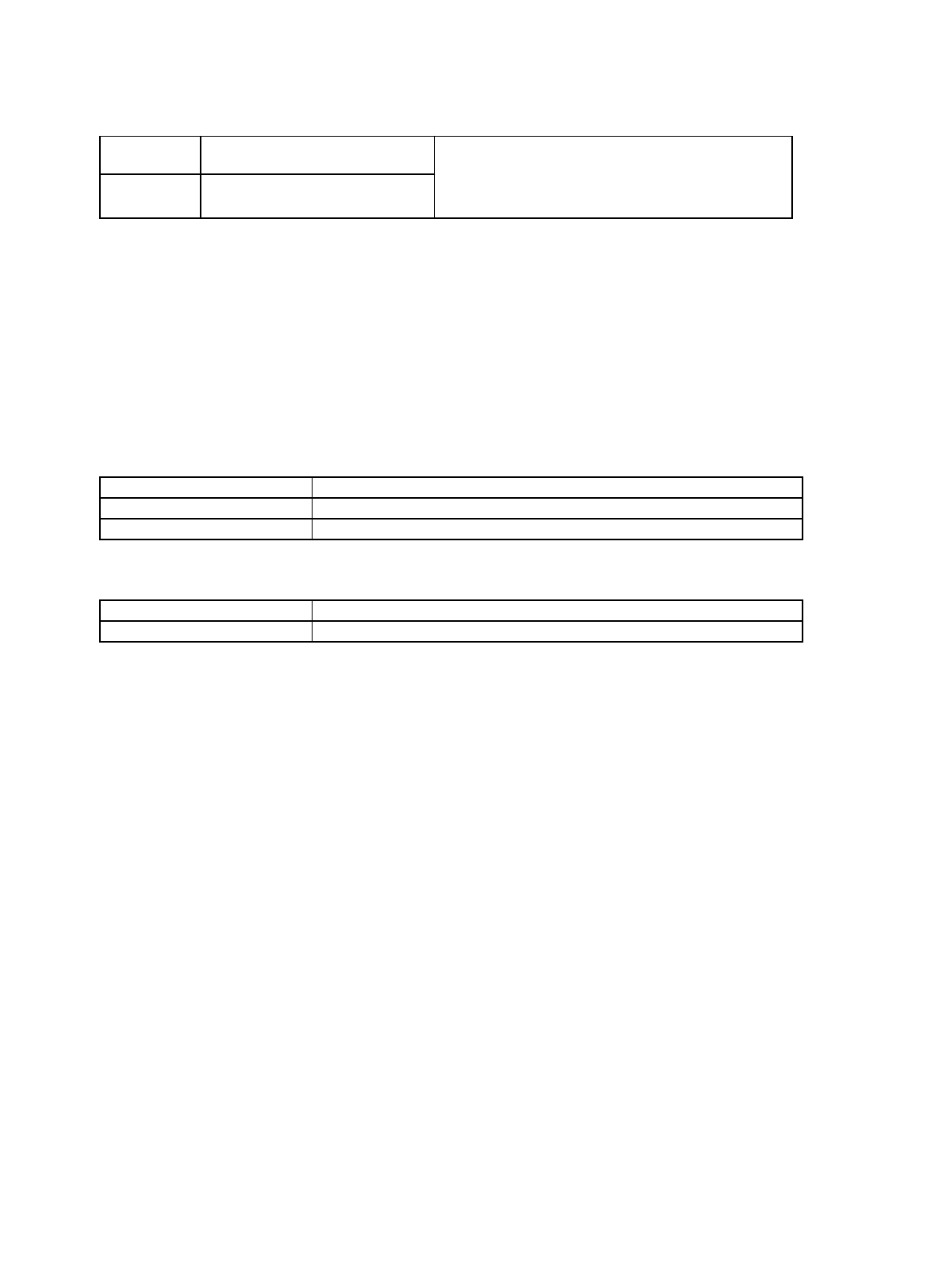

Input Capture 6

#98

Address: 0FFE74h

Interrupt level register (ICR41)

Address: 0469h

Input Capture 7

#99

Address: 0FFE70h

Interrupt request permission bit (ICE0), (CE1)

Disable interrupts Set to “0”

Enable interrupts Set to “1”

Interrupt request bit (ICP0), (ICP1)

Interrupt request clear Write “0”