Memory Management Unit (MMU)

84

NS9750 Hardware Reference

First-level fetch

Bits [31:14] of the TTB register are concatenated with bits [31:20] of the MVA to

produce a 30-bit address.

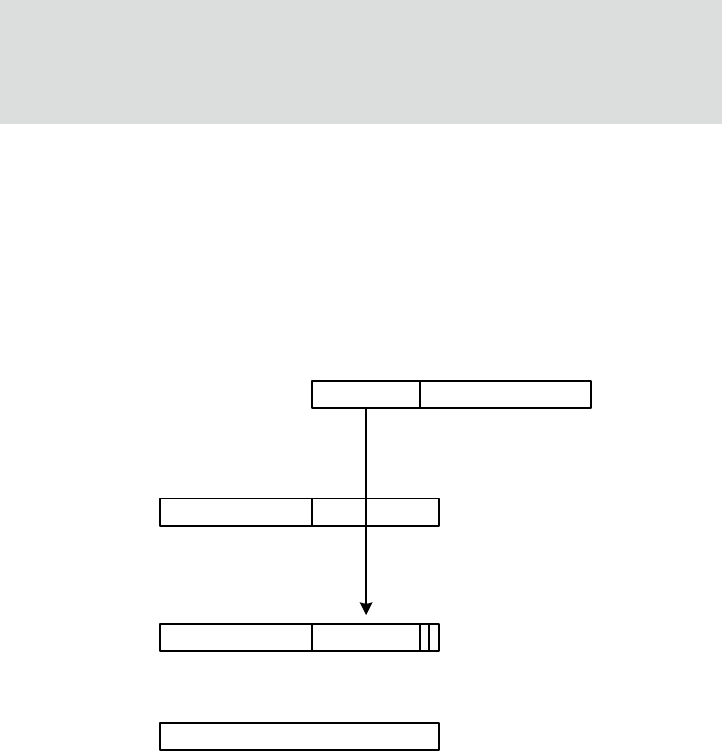

Figure 26 shows the concatenation and address:

Figure 26: Accessing translation table first-level descriptors

This address selects a 4-byte translation table entry. This is a first-level descriptor for

either a section or a page.

First-level descriptor

The first-level descriptor returned is a section description, a coarse page table

descriptor, a fine page table descriptor, or is invalid. Figure 27 shows the format of a

first-level descriptor.

A section descriptor provides the base address of a 1 MB block of memory.

The page table descriptors provide the base address of a page table that contains

second-level descriptors. There are two page-table sizes:

Coarse page tables, which have 256 entries and split the 1 MB that the

table describes into 4 KB blocks.

Modified virtual address

31 20 19 0

Table index

Translation table base

31 14 13 0

Translation base

31 14 13 0

Translation base Table index 00

1

2

31 0

First-level descriptor