www.digiembedded.com

63

Working with the CPU

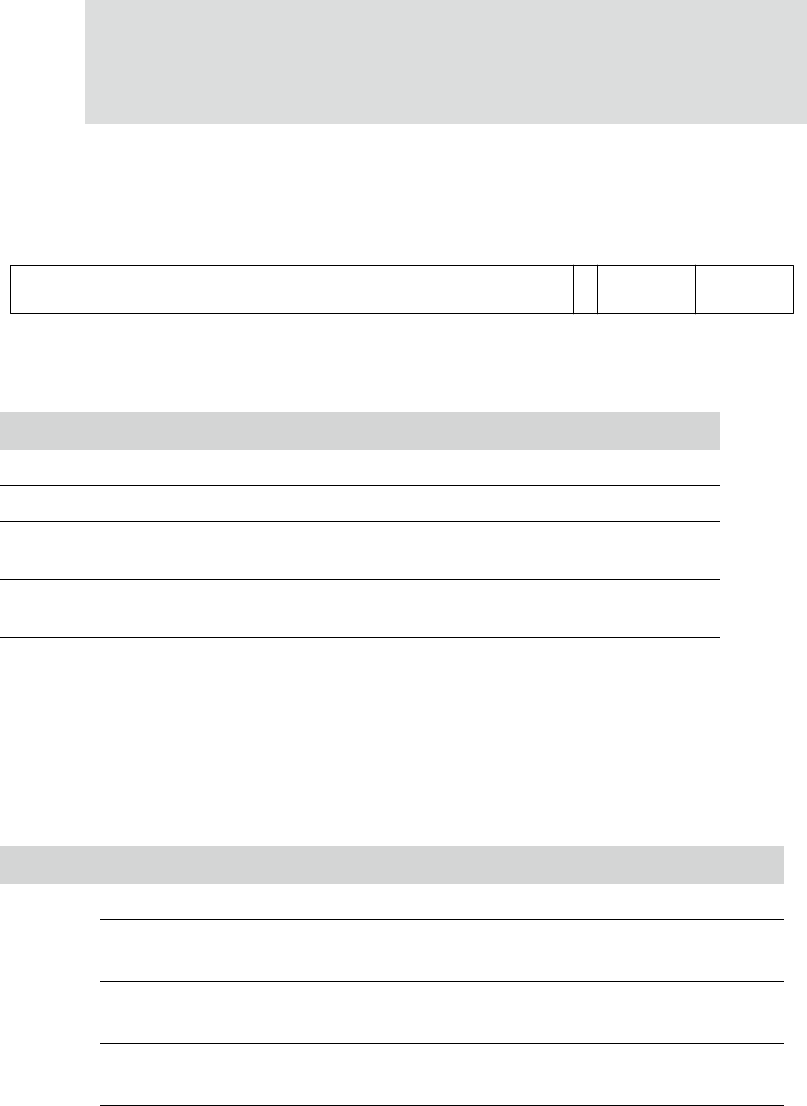

Figure 16 shows the format of the Fault Status registers. Table 24 describes the Fault

Status register bits.

Figure 16: Fault Status registers format

Table 25 shows the encodings used for the status field in the Fault Status register, and

indicates whether the domain field contains valid information. See "MMU faults and

CPU aborts" on page 95 for information about MMU aborts in Fault Address and Fault

Status registers.

Bits Description

[31:9]

UNPREDICTABLE/SHOULD BE ZERO

[8] Always reads as zero. Writes are ignored.

[7:4] Specifies which of the 16 domains (D15–D0) was being accessed when a data

fault occurred.

[3:0] Type of fault generated. (See "Memory Management Unit (MMU)," beginning

on page 78.)

Table 24: Fault Status register bit description

Priority Source Size Status Domain

Highest Alignment N/A

0b00x1

Invalid

External abort on translation First level

Second level

0b1100

0b1110

Invalid

Valid

Translation Section page

0b0101

0b0111

Invalid

Valid

Domain Section page

0b1001

0b1011

Valid

Valid

Permission Section page

0b1101

0b1111

Valid

Valid

Table 25: Fault Status register status field encoding

31 0987 43

0

UNP/SBZ Domain Status