USB Device Endpoint FIFO Control and Data registers

778

NS9750 Hardware Reference

FIFO Interrupt Enable 2 register

Address: 9010 3024

Register bit assignment

D07 R/W ACK3 0 Generate an interrupt when ACK3 in FIFO Interrupt

Status 1 register is asserted.

D06 R/W NACK3 0 Generate an interrupt when NACK3 in FIFO Interrupt

Status 1 register is asserted.

D05 R/W ERROR3 0 Generate an interrupts when ERROR3 in FIFO Interrupt

Status 1 register is asserted.

D04:00 N/A Reserved N/A Not valid in DMA mode.

Bits Access Mnemonic Reset Description

D31 R/W ACK10 0 Generate an interrupt when ACK10 in FIFO Interrupt

Status 2 register is asserted,

D30 R/W NACK10 0 Generate an interrupt when NACK10 in FIFO Interrupt

Status 2 register is asserted.

D29 R/W ERROR10 0 Generate an interrupt when ERROR10 in FIFO Interrupt

Status 2 register is asserted.

D28:24 N/A Reserved N/A Not valid in DMA mode.

D23 R/W ACK9 0 Generate an interrupt when ACK9 in FIFO Interrupt

Status 2 register is asserted.

D22 R/W NACK9 0 Generate an interrupt when NACK9 in FIFO Interrupt

Status 2 register is asserted.

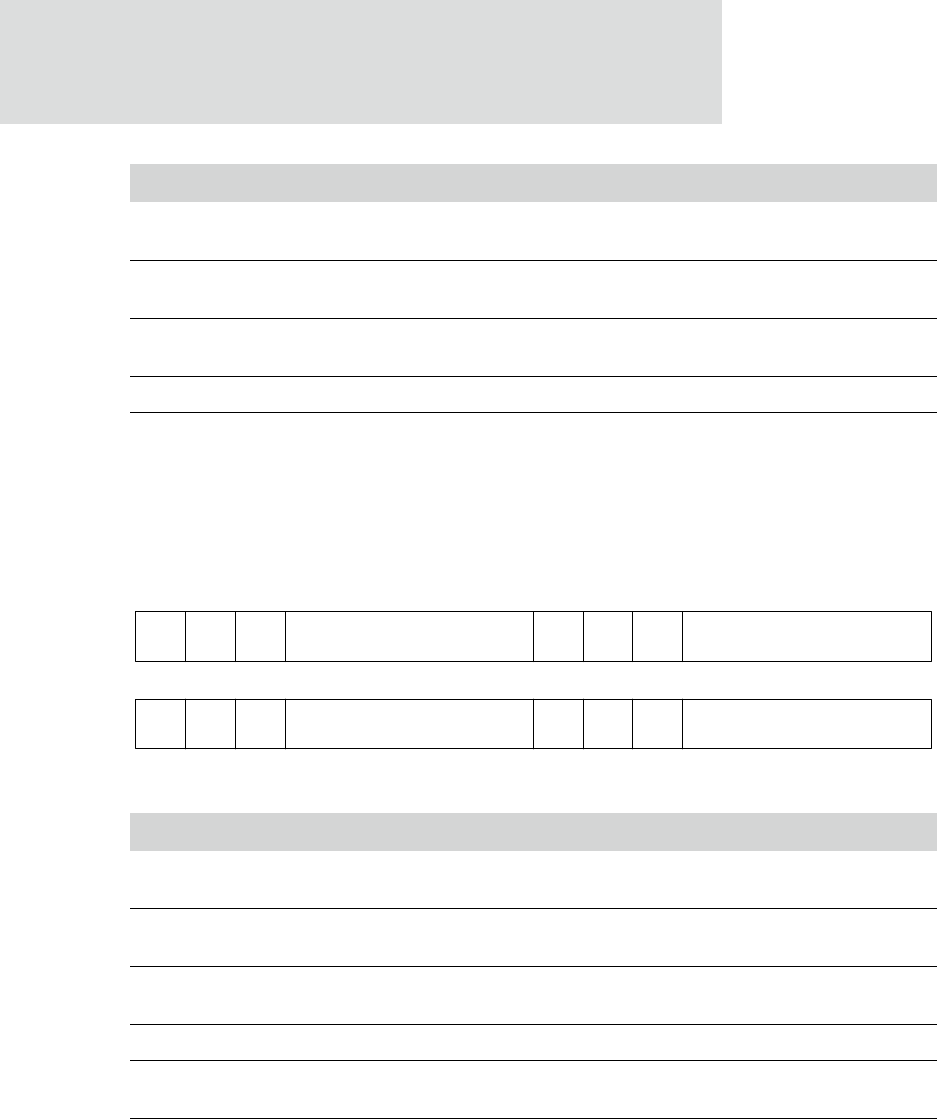

Table 456: FIFO Interrupt Enable 2 register

Bits Access Mnemonic Reset Description

Table 455: FIFO Interrupt Enable 1 register

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved

ERROR

8

Reserved

ACK8

NACK

8

Reserved

ACK7

NACK

7

ERROR

7

ACK

10

NACK

10

ERROR

10

ERROR

9

NACK

9

ACK9

Reserved