Memory Management Unit (MMU)

92

NS9750 Hardware Reference

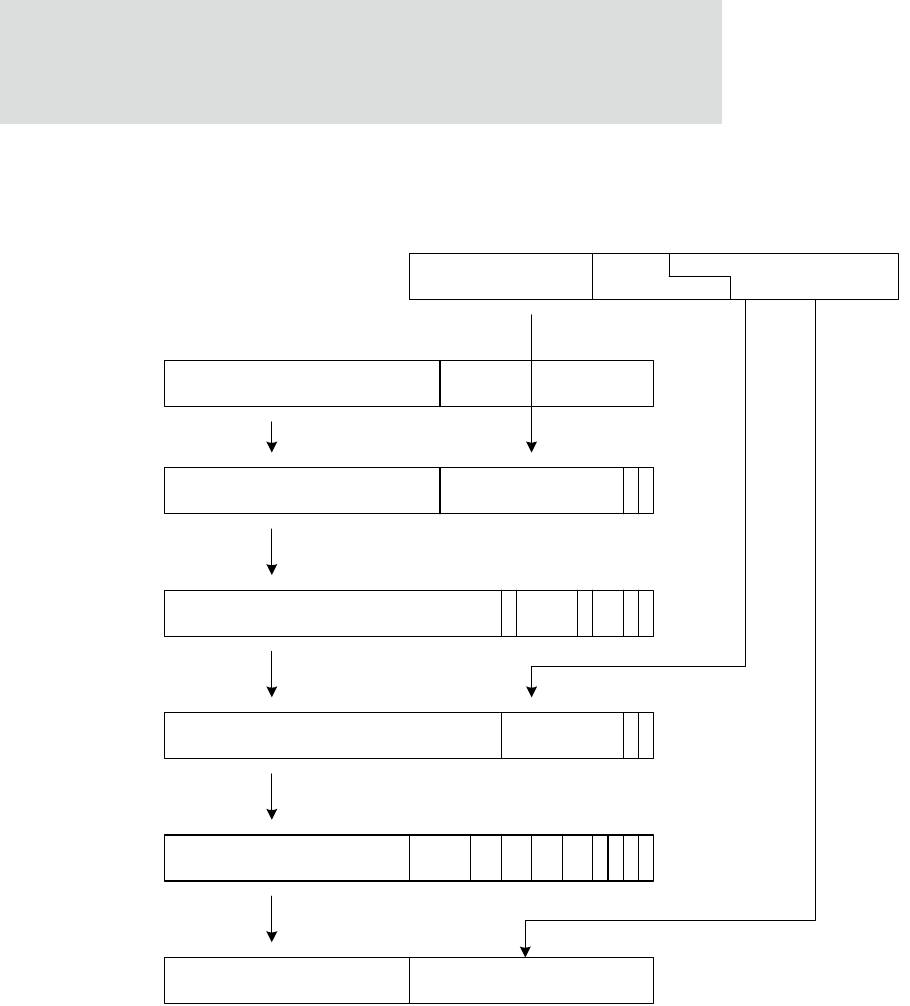

Figure 33: Large page translation from a coarse page table

Because the upper four bits of the page index and low-order four bits of the coarse

page table index overlap, each coarse page table entry for a large page must be

duplicated 16 times (in consecutive memory locations) in the coarse page table.

31 14 13 0

Translation base

1

Translation table base

31 14 13 0

Translation base

2

Table index 0 0

31 2019 0

Table index Page index

First-level descriptor

31 0

Coarse page table base address

2

01

1345

Domain 1

31 0

Coarse page table base address

table index

1615 1211

Modified virtual address

8910

12910

31 1615 121110 9 8 7 6 5 4 3 2 1 0

00L2 table index

01BCAP0AP1AP2AP3Page base address

Page base address

31 01615

Page index

Physical address

Second-level descriptor