SPI timing

830

NS9750 Hardware Reference

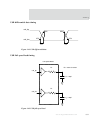

SPI slave mode 0 and 1: 2-byte transfer

(see note 7)

Figure 138: SPI slave mode 0 and 1 (2-byte transfer)

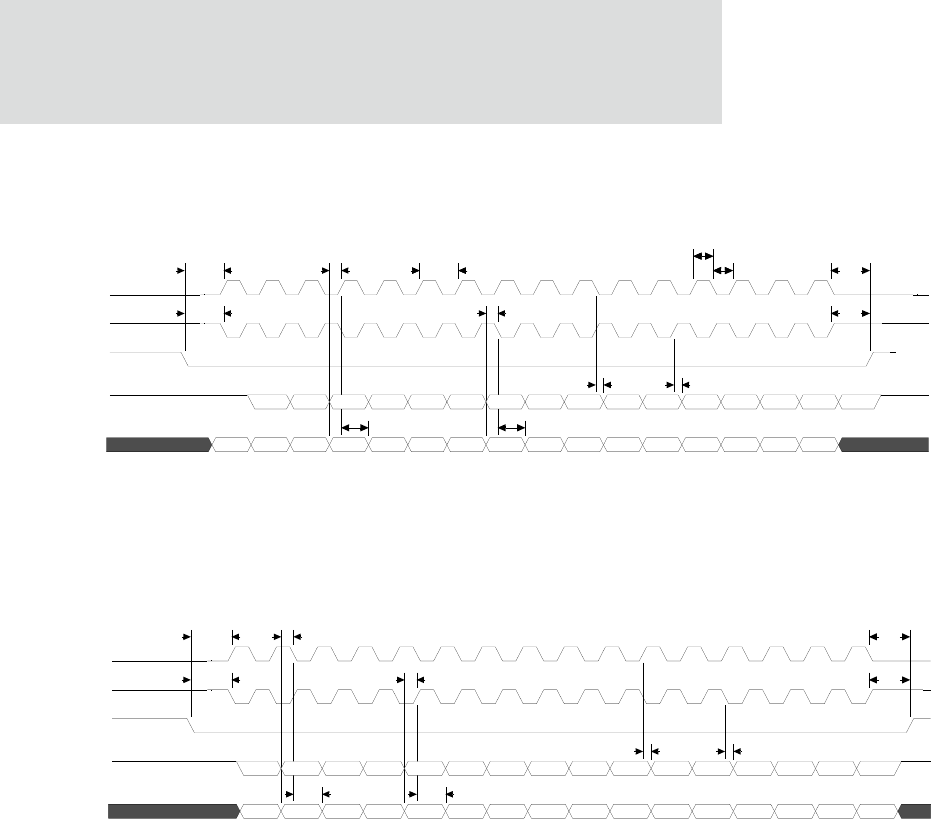

SPI slave mode 2 and 3: 2-byte transfer

(see note 7)

Figure 139: SPI slave mode 2 and 3 (2-byte transfer)

MSB LSB MSB LSB

MSB LSB MSB LSB

SP19SP17

SP21SP20

S23SP18SP15

S22SP25SP25

SP24SP24

SP26SP26SP16SP14

SPI CLK In (Mode 0)

SPI CLK In (Mode 1)

SPI Enable

SPI Data Out

SPI Data In

MSB LSB MSB LSB

MSB LSB MSB LSB

SP19SP17

SP21SP20

S23SP18SP15

S22SP16SP14

SPI CLK In (Mode 2)

SPI CLK In (Mode 3)

SPI Enable

SPI Data Out

SPI Data In