System control processor (CP15) registers

56

NS9750 Hardware Reference

R0: Cache type register

R0: Cache type is a read-only register that contains information about the size and

architecture of the instruction cache (ICache) and data cache (DCache) enabling

operating systems to establish how to perform operations such as cache cleaning and

lockdown. See "Cache features" on page 105 for more information about cache.

You can access the cache type register by reading CP15 register R0 with the

opcode_2

field set to 1. Note this example:

MRC p15, 0, Rd, c0, c0, 1; returns cache details

Figure 12 shows the format of the cache type register. Table 21 describes the fields in

the register.

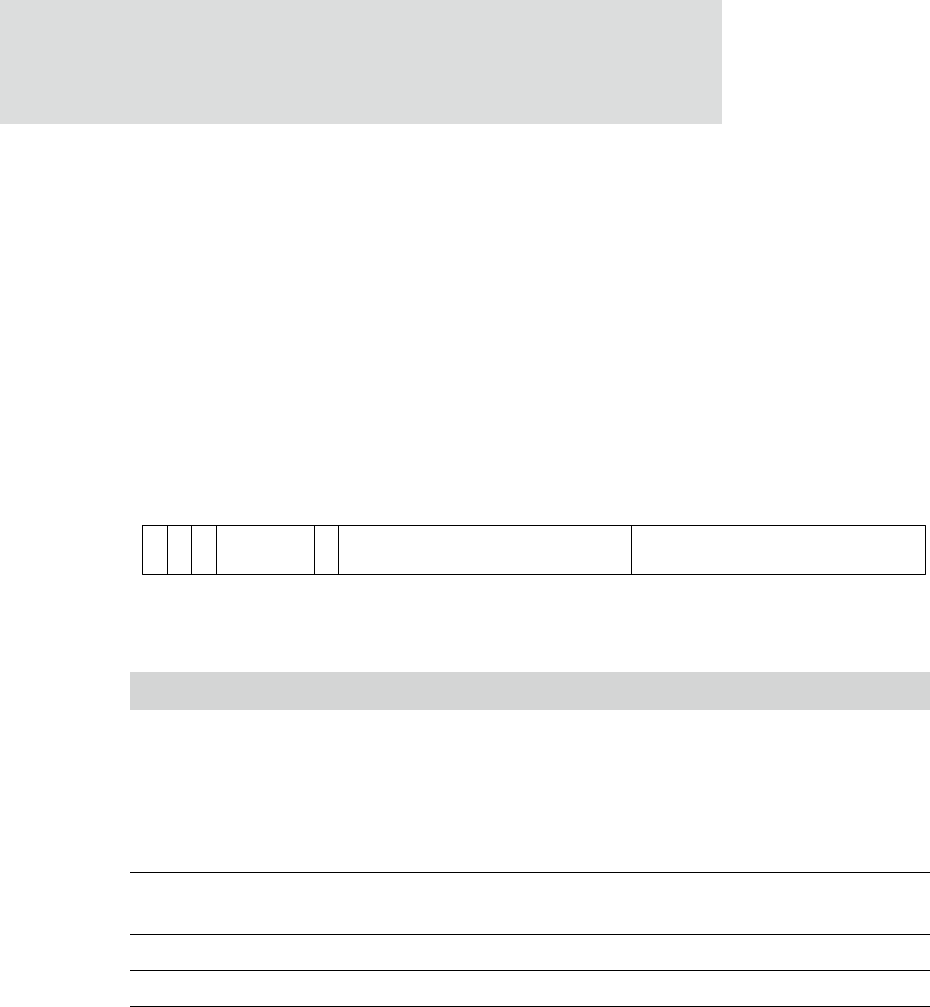

Figure 12: Cache type register format

Field Description

Ctype Determines the cache type, and specifies whether the cache supports lockdown and how it is

cleaned. Ctype encoding is shown below; all unused values are reserved.

Value: 0b1110

Method: Writeback

Cache cleaning: Register 7 operations (see "R7: Cache Operations register" on page 64)

Cache lockdown: Format C (see "R9: Cache Lockdown register" on page 69)

S bit Specifies whether the cache is a unified cache (S=0) or separate ICache and DCache (S=1).

Will always report separate ICache and DCache for NS9750.

Dsize Specifies the size, line length, and associativity of the DCache.

Isize Species the size, length and associativity of the ICache.

Table 21: Cache type register field definition

Ctype

0S

Dsize

31 28 25 24 23 12

00

Isize