Serial port control and status registers

618

NS9750 Hardware Reference

Bits Access Mnemonic Reset Description

D31:28 R MATCH 0x0 Match bit

[31] Match1

[30] Match2

[29] Match3

[28] Match4

Set when a match character in the Receive Match register

is configured at the same time that the enable receive data

match bit is set in Serial Channel Control Register B (see

"RDM" on page 616). The match bit indicates that a data

match was found in the receive data stream, and the

current receive data buffer has been closed. The last

character in the receive data buffer contains the actual

match character found.

In DMA mode, the MATCH field is copied to bits [15:12]

in the DMA buffer descriptor.

D27 R BGAP 0 Buffer GAP timer

Set when the receive buffer GAP timer is set in Serial

Channel Control Register B (see "RBGT" on page 616)

and the timeout value defined in the Receive Buffer GAP

Timer register has expired. This bit indicates that the

maximum allowed time has passed since the first byte was

placed into the receive data buffer. The receive data buffer

is closed under this condition.

In DMA mode, this field is copied to bit [11] in the DMA

buffer descriptor.

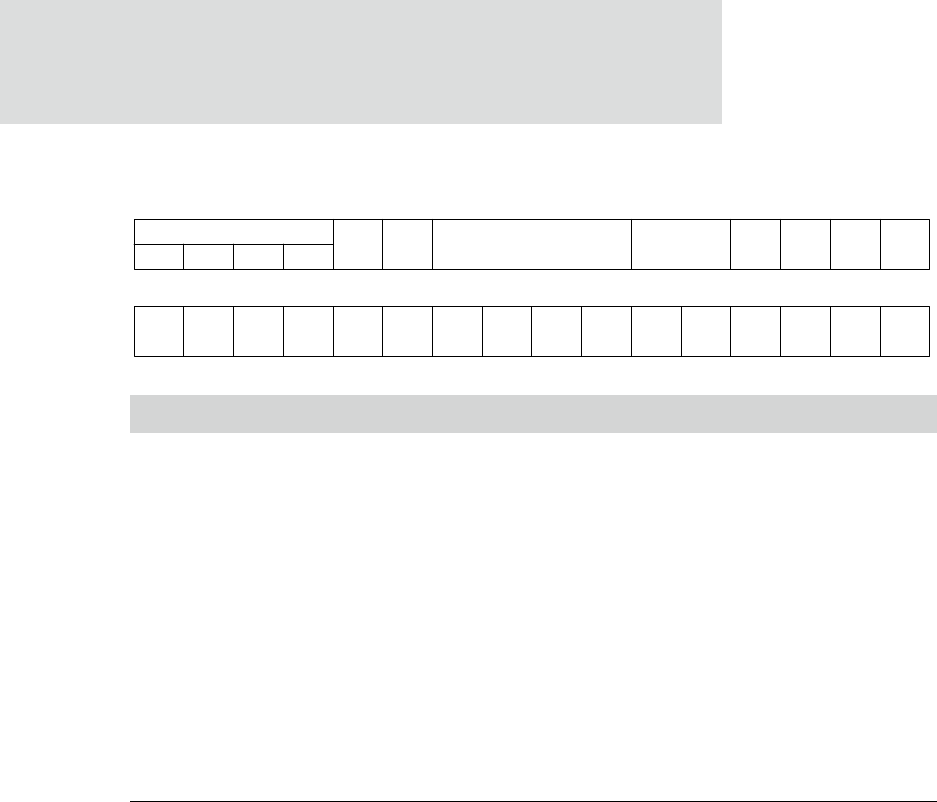

Table 369: Serial Channel B/A/C/D Status Register A

CTSI

T

EMPTY

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

CGAPBGAP RXFDB DCD

Match

Not used

RBRK DSRI THALF

1234

RI DSR CTS

RFE RPE ROVER RRDY RHALF RBC RFS DCDI RII TRDY

Not

used