Memory Management Unit (MMU)

90

NS9750 Hardware Reference

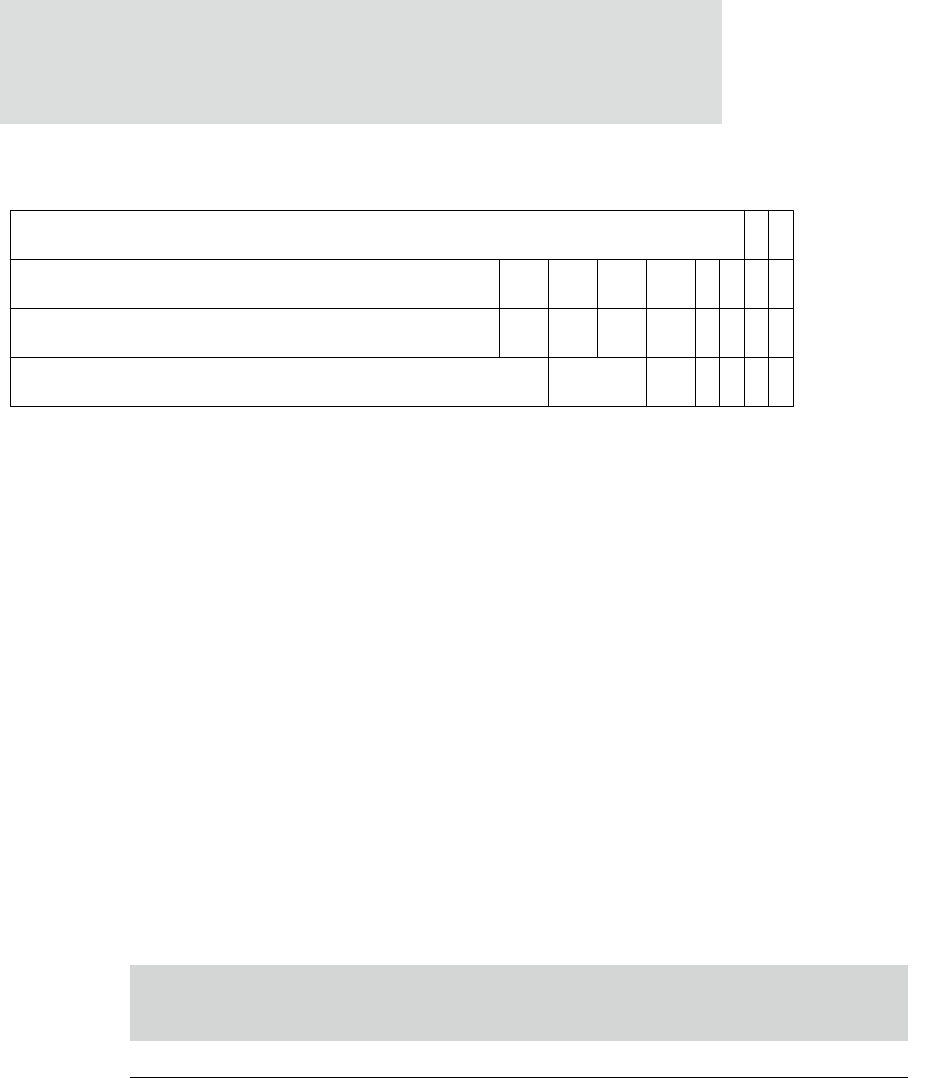

Figure 32: Second-level descriptor

A second-level descriptor defines a tiny, small, or large page descriptor, or is invalid:

A large page descriptor provides the base address of a 64 KB block of

memory.

A small page descriptor provides the base address of a 4 KB block of

memory.

A tiny page descriptor provides the base address of a 1 KB block of memory.

Coarse page tables provide base addresses for either small or large pages. Large page

descriptors must be repeated in 16 consecutive entries. Small page descriptors must

be repeated in each consecutive entry.

Fine page tables provide base addresses for large, small, or tiny pages. Large page

descriptors must be repeated in 64 consecutive entries. Small page descriptors must

be repeated in four consecutive entries. Tiny page descriptors must be repeated in

each consecutive entry.

Table 37 describes the second-level descriptor bit assignments.

31 16 15 12 11 10 9 8 012345

00

0

0

1

1

11

CB

AP0Large page base address

Small page base address

Tiny page base address

76

C

C

B

B

AP0

AP

AP1

AP1

AP2

AP2

AP3

AP3

Fault

Large page

Small page

Tiny page

Bits

Large Small Tiny Description

[31:16] [31:12] [31:10] Form the corresponding bits of the physical address.

[15:12] --- [9:6]

SHOULD BE ZERO

Table 37: Second-level descriptor bits