Serial port control and status registers

610

NS9750 Hardware Reference

The configuration registers for serial controller C are located at 0x9030_0000; the

configuration registers for serial controller D are located at

0x9030_0040. Table 366

shows a single, two-channel address map for serial controllers C and D.

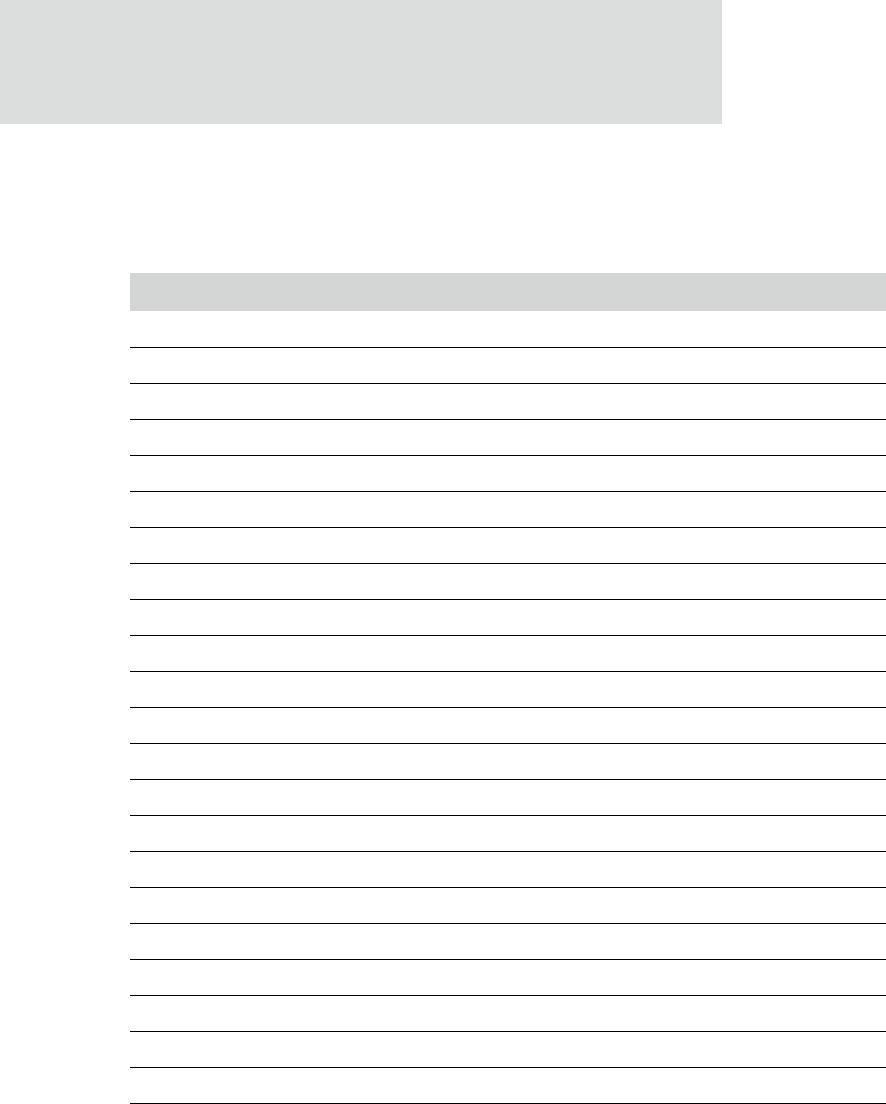

Address Description

9030 0000 Channel C Control Register A

9030 0004 Channel C Control Register B

9030 0008 Channel C Status Register A

9030 000C Channel C Bit-Rate register

9030 0010 Channel C FIFO Data register

9030 0014 Channel C Receive Buffer Gap Timer

9030 0018 Channel C Receive Character Gap Timer

9030 001C Channel C Receive Match register

9030 0020 Channel C Receive Match Mask register

9030 0034 Channel C Flow Control register

9030 0038 Channel C Flow Control Force register

9030 0040 Channel D Control Register A

9030 0044 Channel D Control Register B

9030 0048 Channel D Status Register A

9030 004C Channel D Bit-Rate register

9030 0050 Channel D FIFO Data register

9030 0054 Channel D Receive Buffer Gap Timer

9030 0058 Channel D Receive Character Gap Timer

9030 005C Channel D Receive Match register

9030 0060 Channel D Receive Match Mask register

9030 0074 Channel D Flow Control register

9030 0078 Channel D Flow Control Force register

Table 366: Serial channel C & D configuration registers