www.digiembedded.com

405

PCI-to-AHB Bridge

PCI-to-AHB bridge functionality

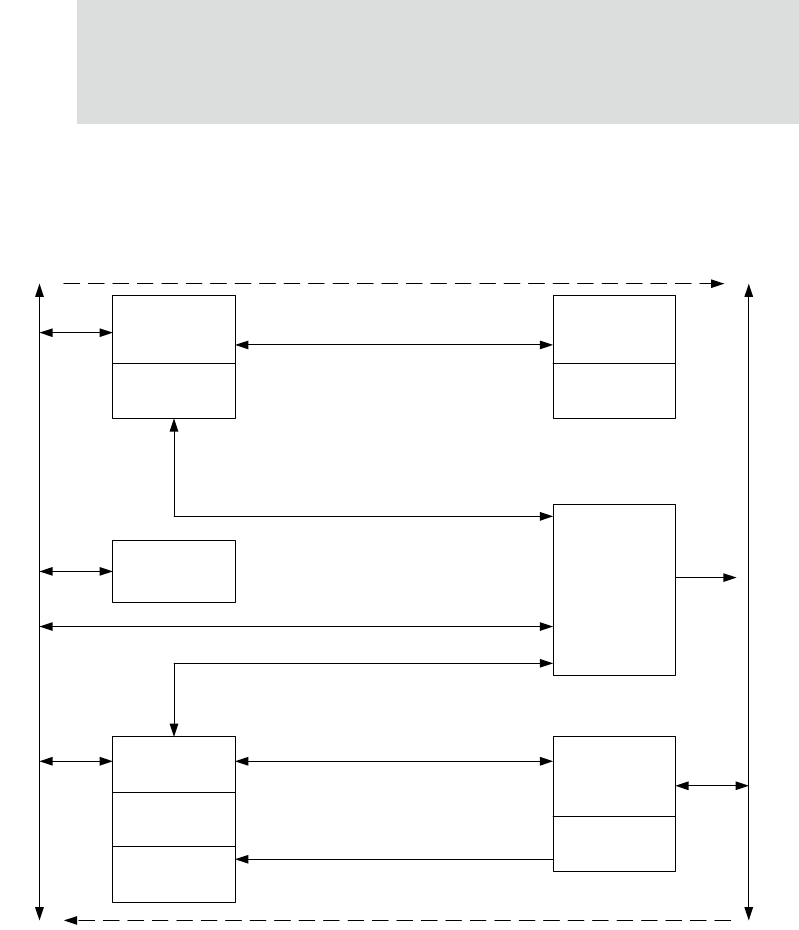

Figure 71 shows the PCI-to-AHB bridge. Downstream transactions are those initiated

on the AHB bus; upstream transactions are those initiated on the PCI bus.

Figure 71: PCI-to-AHB bridge diagram

AHB master interface

The AHB master interface block controls the bridge’s access to the AHB bus as a

master, and is used for reads and writes to the AHB bus that are initiated on the PCI

bus by an external PCI bus master. The requests are transferred to the AHB master

from the PCI target interface. PCI writes are posted in the dual 64-byte PCI target

write buffer. AHB read data is stored in the 64-byte AHB master read buffer before

PCI target

PCI target

write buffer

32x32

PCI bus

arbiter

PCI/Bridge

Config &

Status

registers

AHB master

AHB master

read buffer

16x32

AHB slave/

target

AHB target

write buffer

32x32

PCI master

read buffer

16x32

PCI master

write buffer

32x32

PCI master

Downstream

Upstream

Bus/

Req

grant

Interrupt

Note: The PCI Bus arbiter is not part

of the bridge. It is a separate module

shown here for illustration. It's use is

optional.

PCI bus

AHB bus