www.digiembedded.com

327

Ethernet Communication Module

Transmit packet processor

Transmit frames are transferred from system memory to the transmit packet

processor into a 256-byte TX_FIFO. Because various parts of the transmit frame can

reside in different buffers in system memory, several buffer descriptors can be used

to transfer the frame.

All buffer descriptors (that is, up to 64) are found in a local TX buffer descriptor RAM.

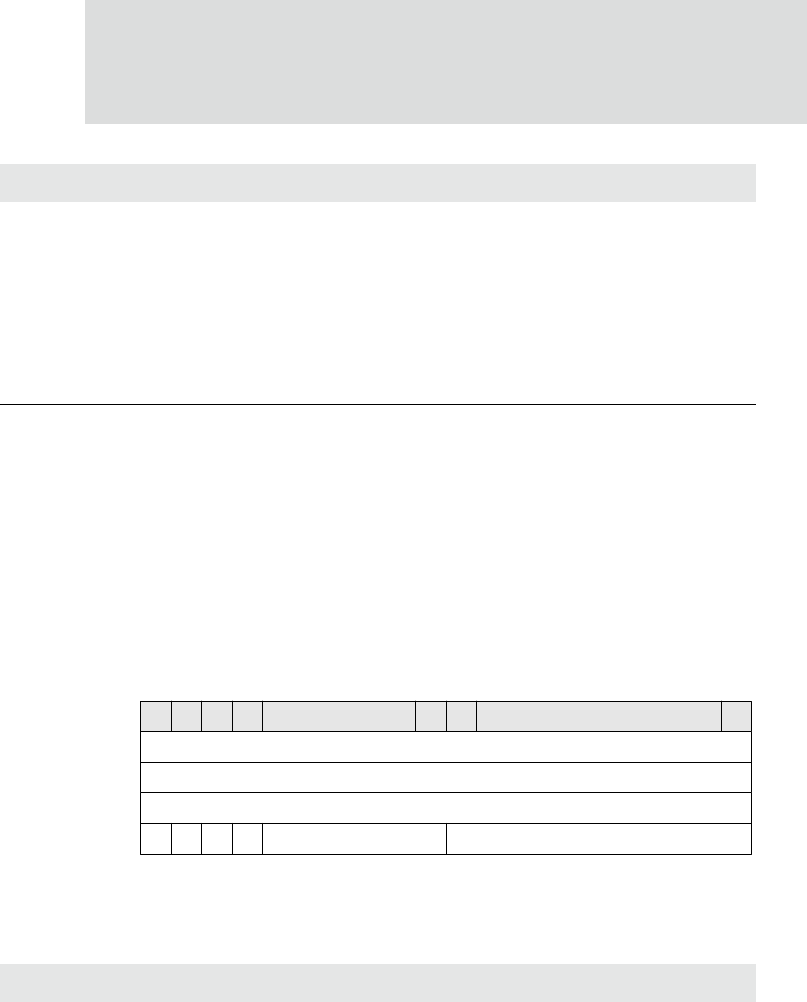

Figure 67 shows the transmit buffer descriptor format.

Figure 67: Transmit buffer descriptor format

Buffer length This is a dual use field:

When the buffer descriptor is read from system memory, buffer length

indicates the maximum sized frame, in bytes, that can be stored in this

buffer ring.

When the RX_RD logic writes the descriptor back from the receive status

FIFO into system memory at the end of the frame, the buffer length is the

actual frame length, in bytes.Only the lower 11 bits of this field are valid,

since the maximum legal frame size for Ethernet is 1522 bytes.

Field Description

Field Description

W

WRAP bit, which, when set, tells the TX_WR logic that this is the last buffer

descriptor within the continuous list of descriptors in the TX buffer descriptor

RAM. The next buffer descriptor is found using the initial buffer descriptor

pointer in the TX Buffer Descriptor Pointer register (TXPTR; see "TX Buffer

Descriptor Pointer register," beginning on page 389).

When the

WRAP bit is not set, the next buffer descriptor is located at the next

entry in the TX buffer descriptor RAM.

Destination Address (not used)

Buffer Length (11-bits used)

Status

Source Address

0

OFFSET + 0

OFFSET + 4

OFFSET + 8

OFFSET + C

FILW Reserved

31 151630 29 28