Memory Management Unit (MMU)

86

NS9750 Hardware Reference

Section descriptor

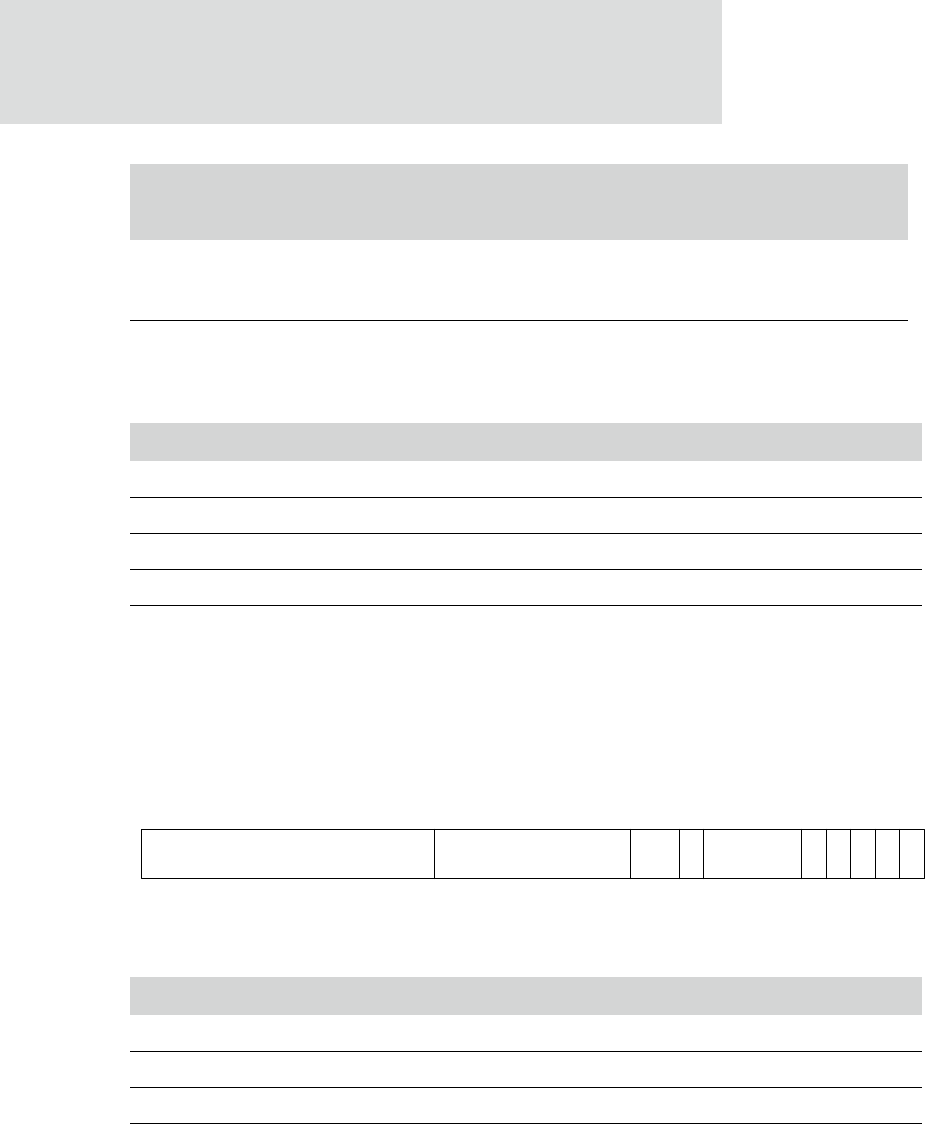

A section descriptor provides the base address of a 1 MB block of memory. Figure 28

shows the section descriptor format. Table 34 describes the section descriptor bits.

Figure 28: Section descriptor

[1:0] [1:0] [1:0] These bits indicate the page size and validity, and are

interpreted as shown in Table 33, “Interpreting first-level

descriptor bits [1:0],” on page 86.

Value Meaning Description

0 0 Invalid Generates a section translation fault.

0 1 Coarse page table Indicates that this is a coarse page table descriptor.

1 0 Section Indicates that this is a section descriptor.

1 1 Fine page table Indicates that this is a fine page table descriptor.

Table 33: Interpreting first-level descriptor bits [1:0]

Bits Description

[31:20] Forms the corresponding bits of the physical address for a section.

[19:12] Always written as 0.

[11:10] Specify the access permissions for this section.

[09 Always written as 0.

Table 34: Section descriptor bits

Bits

Section Coarse Fine Description

Table 32: Priority encoding of fault status

Section base address SBZ

S

B

Z

AP Domain 1 1 0CB

10234589101112192031