www.digiembedded.com

349

Ethernet Communication Module

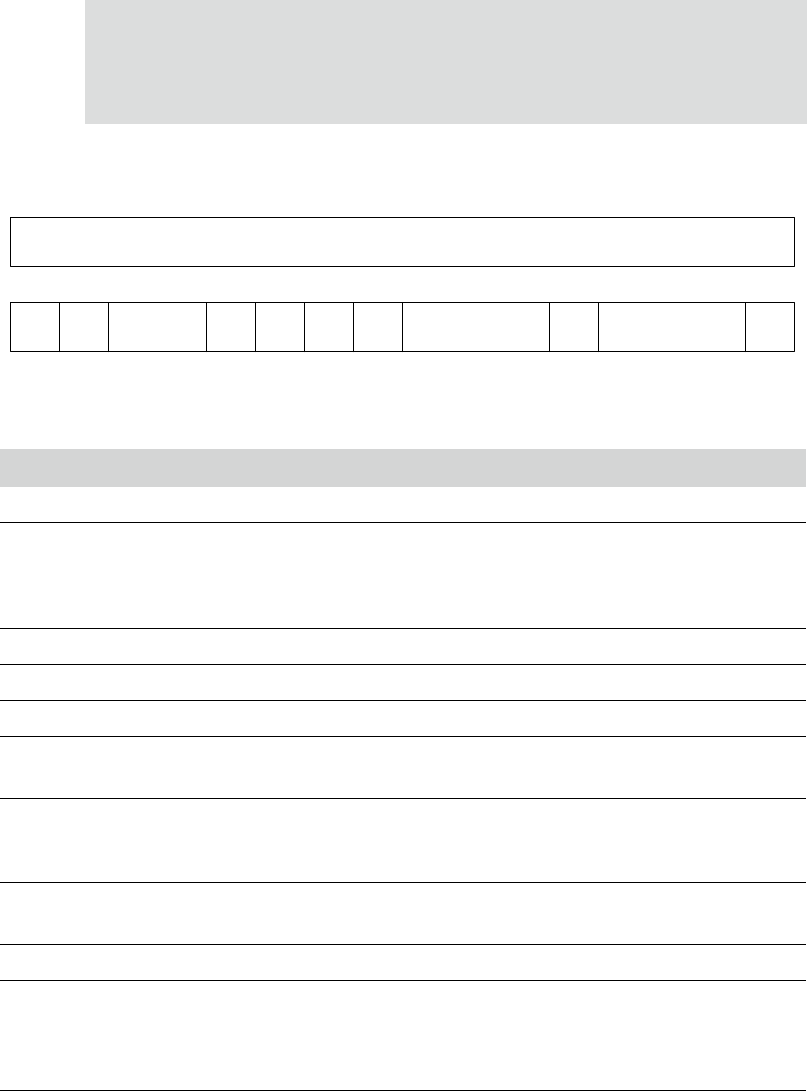

Register bit assignment

Bits Access Mnemonic Reset Description

D31:16 N/A Reserved N/A N/A

D15 R/W SRST 1 Soft reset

Set this bit to 1 to reset the

RX_WR, TX_RD, MAC

(except host interface), SAL (except host interface), and

RMII modules.

D14 R/W Not used 0 Always write as 0.

D13:12 N/A Reserved N/A N/A

D11 N/A Not used 0 Always write as 0.

D10 R/W RPERFUN 0 Reset PERFUN

Set this bit to 1 to put the MAC receive logic into reset.

D09 R/W RPEMCST 0 Reset PEMCS/TX

Set this bit to 1 to put the MAC control sublayer/

transmit domain logic into reset.

D08 R/W RPETFUN 0 Reset PETFUN

Set this bit to 1 to put the MAC transmit logic into reset.

D07:05 N/A Reserved N/A N/A

D04 R/W LOOPBK 0 Internal loopback

Set this bit to 1 to cause the MAC transmit interface to

be internally looped back to the MAC receive interface.

Clearing this bit results in normal operation.

D03:01 R/W Not used 0 Always write as 0.

Table 211: MAC Configuration Register #1

Reserved

13 12 11 10 9 8 7 6 5 4 3 2 1 015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

ReservedSRST

RPER

FUN

RPE

MCST

RPET

FUN

Reserved

LOOP

BK

RXEN

Not

used

Not used

Not

used