www.digiembedded.com

255

System Control Module

met. See "Arbiter configuration examples" on page 258 for information about

configuring the AHB arbiter.

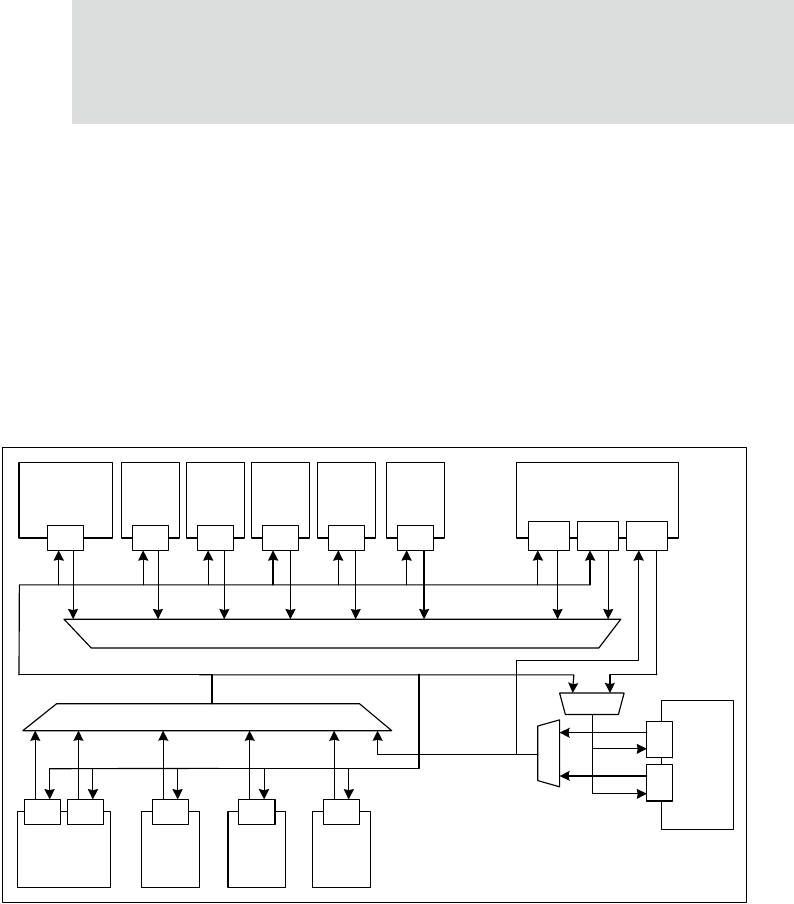

The NS9750 high-speed bus system is split into two subsystems:

High-speed peripheral subsystem: Connects all high-speed peripheral

devices to a port on the external memory controller.

CPU subsystem: Connects the CPU directly to a second port on the external

memory controller.

Figure 60 shows an overview of the NS9750 high-speed bus architecture.

Figure 60: NS9750 bus architecture

The NS9750 high-speed bus contains two arbiters: one for the ARM926 (CPU) and one

for the main bus.

CPU arbiter. Splits the bandwidth 50–50 between the data and instruction

interfaces. If the CPU access is to external memory, no further arbitration is

necessary; the CPU has immediate access to external memory through slave

port 0 on the memory controller. If CPU access is to one of the peripherals

on the main bus, however, the main arbiter will arbitrate the access.

ARM

926

I D

Ethernet

MAC

Slv

PCI

Slv

Bbus

Slv

LCD

Slv

Memory

Controller

Reg

Slv

Slv 1

Ethernet

MAC

Tx Rx

PCI

Mst

Bbus

Mst

LCD

Mst

Master Write Mux

Slave Read Mux

PCI

Arb

Slv

SCM

Slv

Slv 0