Static memory controller

146

NS9750 Hardware Reference

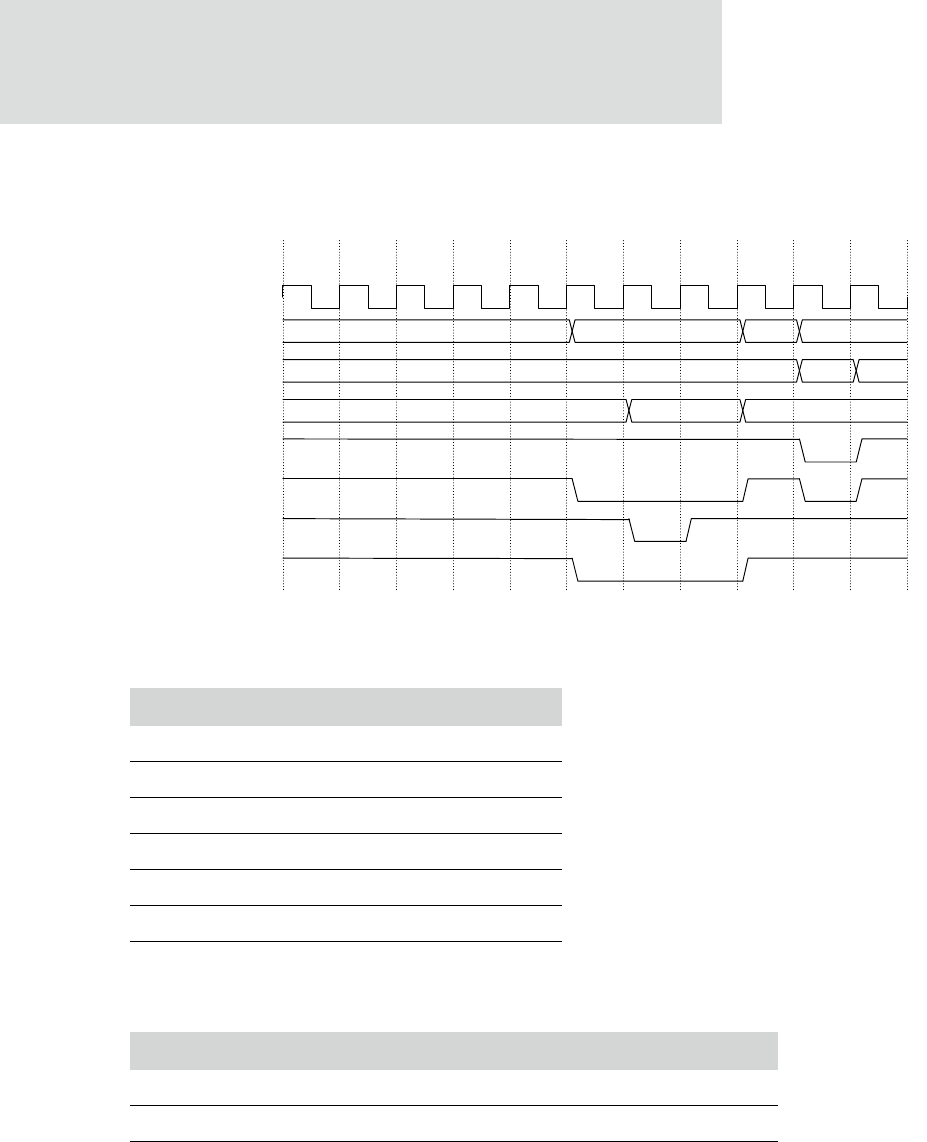

Table 75 provides the timing parameters. Table 76 describes the transactions for

Figure 54.

Figure 54: Write followed by a read (both 0 wait) with no turnaround

Timing parameters Value

WAITRD 0

WAITOEN 0

WAITPAGE N/A

WAITWR 0

WAITWEN 0

WAITTURN 0

Table 75: Static memory timing parameters

Cycle Description

T0 AHB address provided to memory controller.

T0-T1 AHB transaction processing.

T1-T4 Arbitration of memory ports.

Table 76: Write followed by read (both 0 wait) with no turnaround

ADDR

DATAIN

B

STCSOUT_n

WEOUT_n

DATAOUT

COEOUT_n

DATAEN_n

0A

D(B)

D(A)

clk_out

T0 T1 T2 T3 T4 T5 T6 T7 T8 T9 T10