Interrupt controller

268

NS9750 Hardware Reference

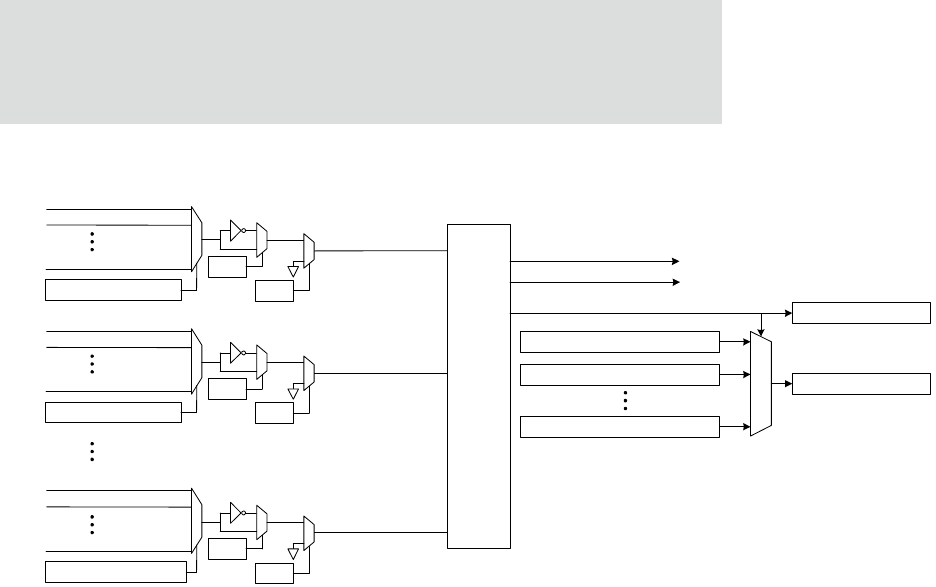

Figure 61: Interrupt controller block diagram

The IRQ interrupts are enabled by the respective enabling bits. Once enabled, the

interrupt source programmed in the Interrupt Configuration register for each priority

level connects the interrupt to one of 32 priority lines going into the priority encoder

block. The priority encoder block has a fixed order, with line 0 as the highest priority.

The interrupt with the highest priority level has its encoded priority level displayed,

to select the appropriate vector for the ISRADDR register (see "ISRADDR register" on

page 288). The CPU, once interrupted, can read the ISRADDR register to get the

address of the Interrupt Service Routine. A read to the ISRADDR register updates the

priority encoder block, which masks the current and any lower priority interrupt

requests. Writing to this address indicates to the priority hardware that the current

interrupt is serviced, allowing lower priority interrupts to become active.

The priority encoder block enables 32 prioritized interrupts to be serviced in nested

fashion. A software interrupt can be implemented by writing to a software interrupt

register. The software interrupt typically is assigned level 1 or level 2 priority.

Interrupt sources

An Interrupt Status register shows the current active interrupt requests. The Raw

Interrupts register shows the status of the unmasked interrupt requests.

Interrupt Source 0

Interrupt Source 1

Interrupt Source 31

Priority Level 1

Interrupt Source ID Reg 1

Interrupt Source 0

Interrupt Source 1

Interrupt Source 31

Priority Level 0 (highest)

Interrupt Source ID Reg 0

Interrupt Source 0

Interrupt Source 1

Interrupt Source 31

Priority Level 31 (lowest)

Interrupt Source ID Reg 31

Priority

Encoder

IRQ

FIQ

Interrupt Vector Address Reg Level 1

Interrupt Vector Address Reg Level 31

Interrupt Vector Address Reg Level 0

Winning Priority Level

ISADDR Reg

Active Interrupt Level Reg

Enable

Invert

Enable

Invert

Enable

Invert