Static memory controller

140

NS9750 Hardware Reference

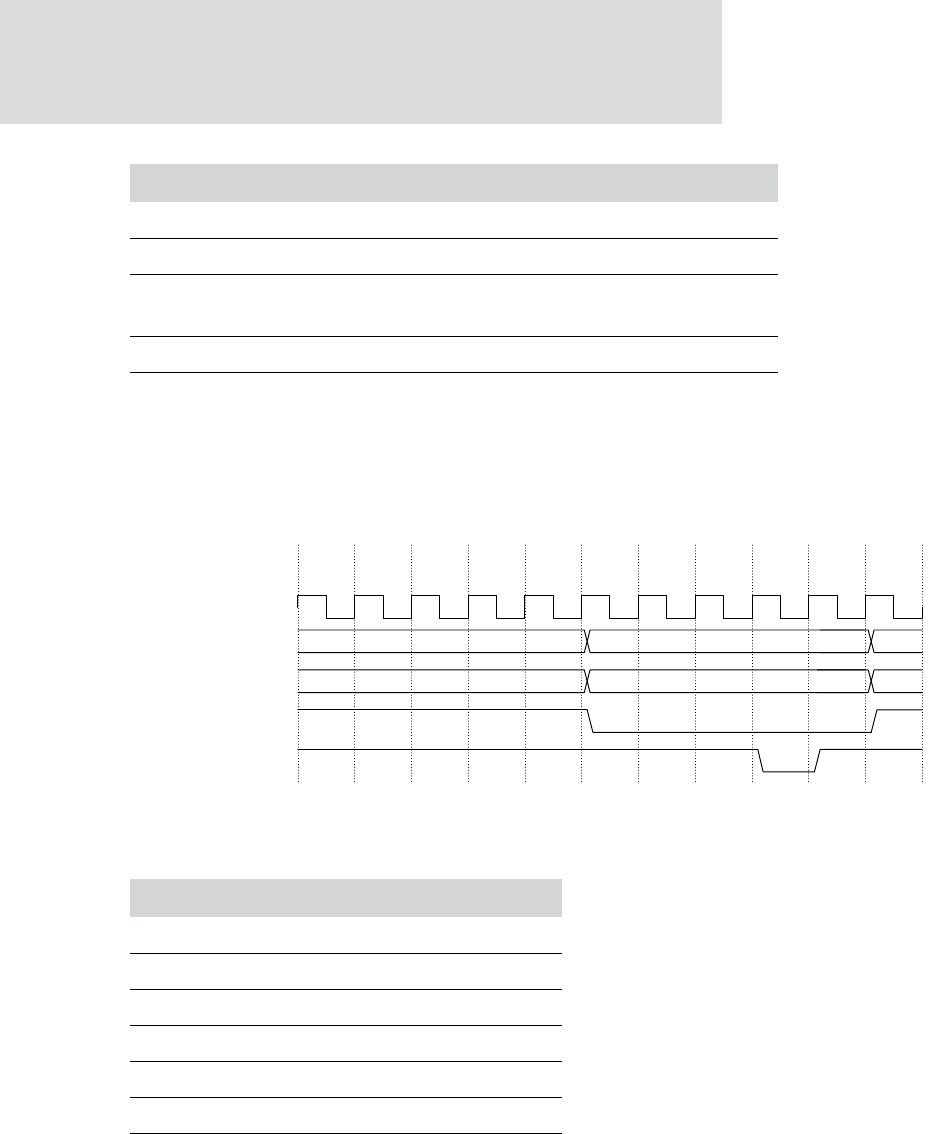

Figure 51 shows a single external memory write transfer with two write enable delay

states (

WAI TWEN =2). One wait state is added. Table 69 provides the timing

parameters.

Figure 51: External memory 2 write enable delay write timing diagram

T6-T7 Wait state 1.

T7-T8 Wait state 2.

T8-T9 Static memory writes the data.

Write enable taken inactive.

T9-T10 Static memory control signals taken inactive.

Timing parameters Value

WAITRD N/A

WAITOEN N/A

WAITPAGE N/A

WAITWR 2

WAITWEN 2

WAITTURN N/A

Table 69: Static memory timing parameters

Cycle Description

Table 68: External memory 2 wait state write

ADDR

DATAOUT

A

STCSOUT_n

D(A)

WEOUT

clk_out

T0 T1 T2 T3 T4 T5 T6 T7 T8 T9 T10