BBus Utility Control and Status registers

540

NS9750 Hardware Reference

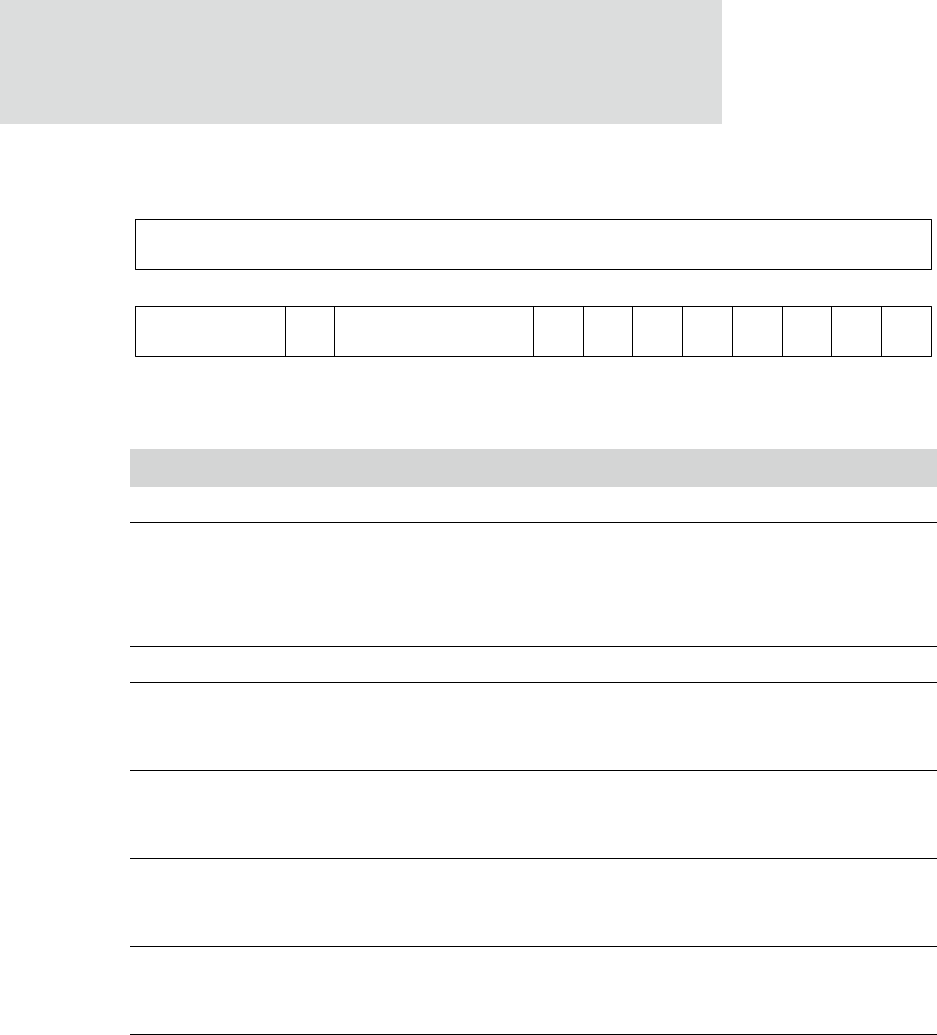

Register bit assignment

Bits Access Mnemonic Reset Description

D31:13 R Not used 0x0 Always read as 0x0

D12 R/W AHBM Reset to the

value

provided on

strapping pin

gpio[44]

AHB bus master

0 Little endian

1 Big endian

D11:08 N/A Reserved N/A N/A

D07 R/W I2C 0 I

2

C controller

0 Little endian

1 Big endian

D06 R/W IEEE1284 0 IEEE 1284 controller

0 Little endian

1 Big endian

D05 R/W SerD 0 Serial controller port D

0 Little endian

1 Big endian

D04 R/W SerC 0 Serial controller port C

0 Little endian

1 Big endian

D03 R/W SerA 0 Serial controller port A

0 Little endian

1 Big endian

Table 332: Endian Configuration register

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Not used

Not used

AHBM Reserved I2C

IEEE

1284

SerD SerC SerA SerB USB DMA