Ethernet front-end module

326

NS9750 Hardware Reference

used is read from system memory and stored in the registers internal to the RX_RD

logic.

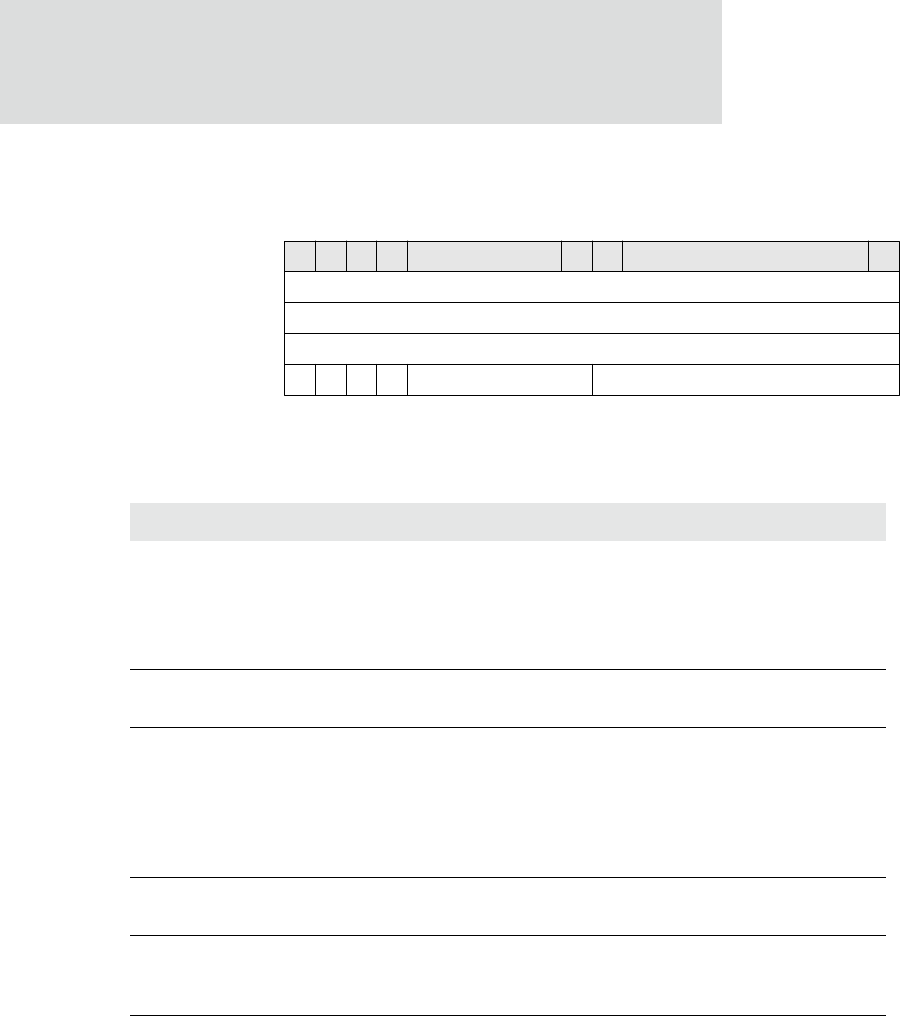

Figure 66: Receive buffer descriptor format

Field Description

W

WRAP bit, which, when set, tells the RX_RD logic that this is the last buffer

descriptor in the ring. In this situation, the next buffer descriptor is found using

the appropriate Buffer Descriptor Pointer register.

When the

WRAP bit is not set, the next buffer descriptor is found using an offset

of

0x10 from the current buffer descriptor pointer.

I When set, tells the RX_RD logic to set RXBUFC in the Ethernet Interrupt Status

register (see page 385) after the frame has been transferred to system memory.

E ENABLE bit, which, when set, tells the RX_RD logic that this buffer descriptor

is enabled. When a new frame is received, pools that do not have the E bit set in

their next buffer descriptor are skipped when deciding in which pool to put the

frame.

The receive processor can use up to four different-sized receive buffers in

system memory.

Buffer pointer 32-bit pointer to the start of the buffer in system memory. This pointer must be

aligned on a 32-bit boundary.

Status Lower 16 bits of the Ethernet Receive Status register. The status is taken from

the receive status FIFO and added to the buffer descriptor after the last word of

the frame is written to system memory.

F When set, indicates the buffer is full. The

RX_RD logic sets this bit after filling

a buffer. The system software clears this bit, as required, to free the buffer for

future use. When a new frame is received, pools that have the F bit set in their

next buffer descriptor are skipped when deciding in which pool to put the frame.

Destination Address (not used)

Buffer Length (11 lower bits used)

Status

Source Address

0

OFFSET + 0

OFFSET + 4

OFFSET + 8

OFFSET + C

FIEW Reserved

31 151630 29 28