www.digiembedded.com

385

Ethernet Communication Module

Ethernet Interrupt Status register

Address: A060 0A10

The Ethernet Interrupt Status register contains status bits for all of the Ethernet

interrupt sources. Each interrupt status bit is assigned to either the RX or TX Ethernet

interrupt; bits D25:16 are assigned to the RX interrupt and D06:00 are assigned to the

TX interrupt.

The bits are set to indicate an interrupt condition, and are cleared by writing a 1 to

the appropriate bit. All interrupts bits are enabled using the Ethernet Interrupt

Enable register (EINTREN). If any enabled bit in the Ethernet Interrupt Status register

is set, its associated Ethernet interrupt to the system is set. The interrupt to the

system is negated when all active interrupt sources have been cleared. If an interrupt

source is active at the same time the interrupt bit is being cleared, the interrupt

status bit remains set and the interrupt signal remains set.

Note:

For diagnostics, software can cause any of these interrupt status bits to

be set by writing a 1 to a bit that is 0.

Register bit assignment

Bits Access Mnemonic Reset Description

D31:26 N/A Reserved N/A N/A

D25 R/C

RXOVFL_DATA

0 Assigned to RX interrupt.

RX data FIFO overflowed. For proper operation, reset

the receive packet processor using the ERX bit in the

Ethernet General Control register when an overflow

condition occurs.

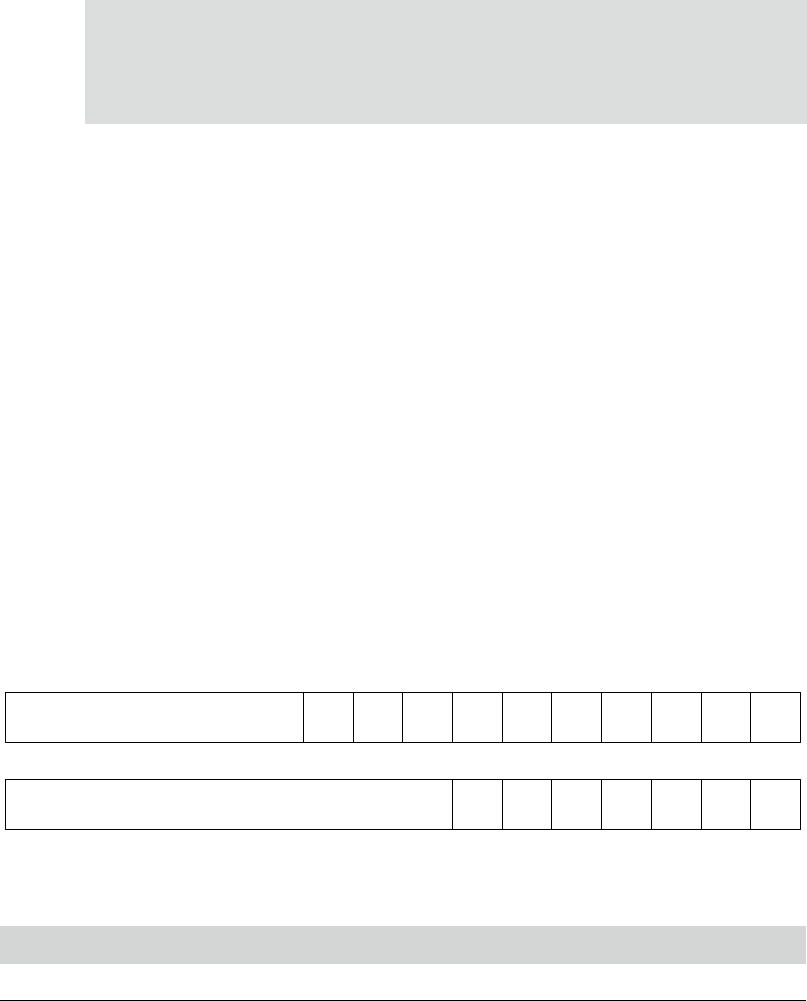

Table 240: Ethernet Interrupt Status register

Reserved

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved

RX

DONE

C

RX

DONE

D

RXNO

BUF

RX

BU

FFUL

RXBR

RX

OVFL_

DATA

RX

OVFL_

STAT

RX

BUFC

RX

DONE

A

RX

DONE

B

ST

OVFL

Not

used

TX

BUFC

TX

BUF

NR

TX

DONE

TX

ERR

TX

IDLE