Serial port control and status registers

624

NS9750 Hardware Reference

Serial Channel B/A/C/D Bit-rate register

Address: 9020 000C / 004C

9030 000C / 004C

The Serial Channel B/A/C/D Bit-rate register contains the serial channel timing

reference control bits and the data rate control bits.

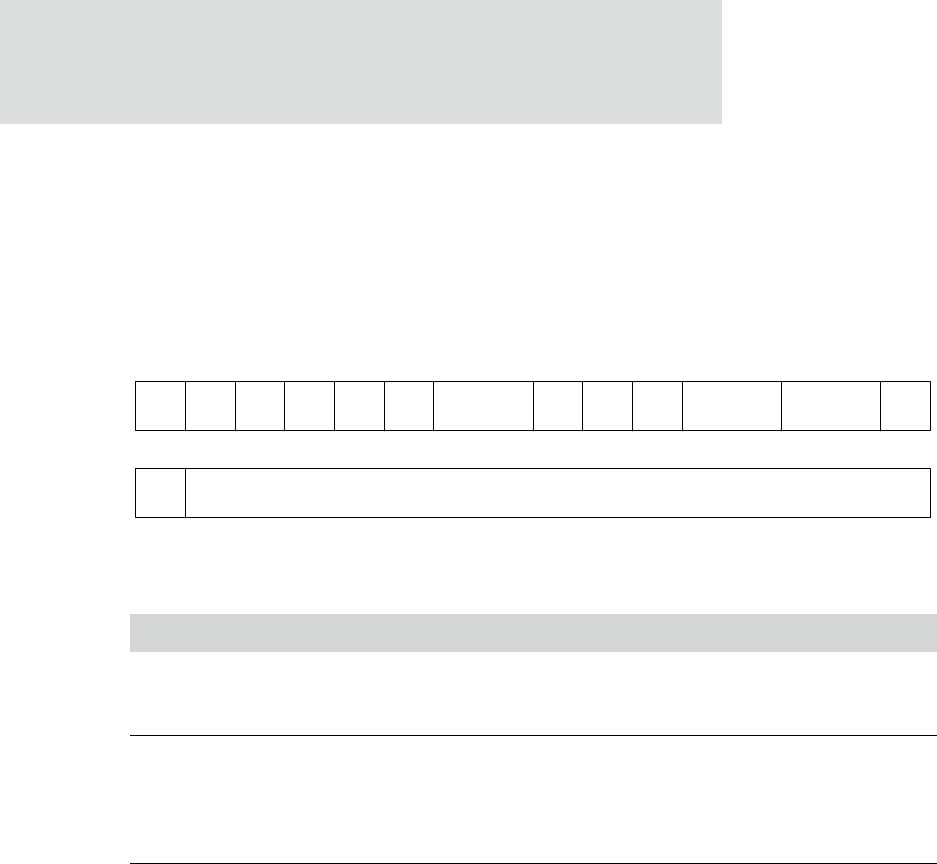

Register bit assignment

Bits Access Mnemonic Reset Description

D31 R/W EBIT 0 Bit-rate generator enable

Enables the internal bit-rate generator when set

to 1.

D30 R/W TMODE 0 Timing mode

Must be set to 1. Use the additional timing configuration

provided by the TDCR and RDCR fields (D[20:19] and

D[18:17] in this register) to configure the channel for 1x,

8x, 16x, or 32x mode.

D29 R/W RXSRC 0 Receive timing source

0 Internal

1 External (input using GPIO pin)

Controls the source of the receiver clock. The receive

clock can be provided by an internal source selected using

the RICS field (see D15).

As an alternative, the receiver clock can be provided by an

input on GPIO pins gpio[6], gpio[14], gpio[22], and

gpio[26] for serial ports B, A, C, and D, respectively.

Table 370: Serial Channel B/A/C/D Bit-rate register

13121110987654321015 14

Not

used

N (divisor value)

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

RXSRC

TX

SRC

TX

EXT

RX

EXT

CLKMUX

TXC

INV

RXC

INV

Rsvd TDCR

Not

used

EBIT

T

MODE

RDCR