PCI timing

820

NS9750 Hardware Reference

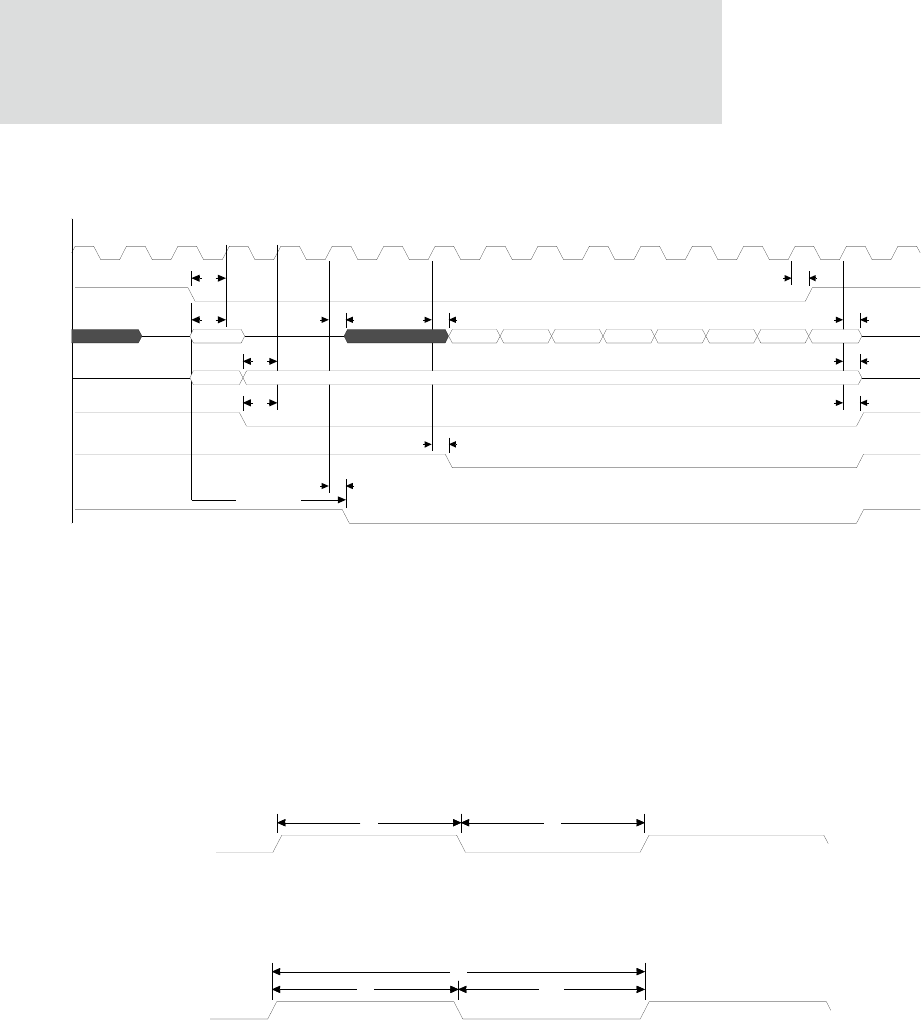

PCI burst read to NS9750 timing

Figure 125: PCI burst read to NS9750 timing

Note:

The functional timing for valid read data on ad[31:0] is just an example. The

actual response time will depend on when the PCI bridge gets access to

the AHB bus internal to NS9750.

PCI clock timing

Figure 126: pci_clock_out timing

Figure 127: pci_clk_in timing

3x pci_clk_in

P1

P1

P3P2

P3P2

P5P1P4P2

P3P2

byte enablescmd

addr data0 data1 data2 data3 data4 data5 data6 data7

Nt

pci_clk_in

frame_n

ad[31:0]

cbe_n[3:0]

irdy_n

trdy_n

devsel_n

P7P7P6P6

pci_clk_out

P10

P8

P10P9P9

P8

pci_clk_in