Requirements

670

NS9750 Hardware Reference

Requirements

Two components are required to run the IEEE 1284 peripheral-to-host interface:

Clock divider. Required to generate the 1284-port operating clock from the

BBus clock. The operating range of the port clock typically is 100 KHz–2

MHz. The clock divider is set using the granularity counter (see "Granularity

Count register" on page 702).

External transceivers. The data flow direction control is provided using a

GPIO pin under software control.

Overview

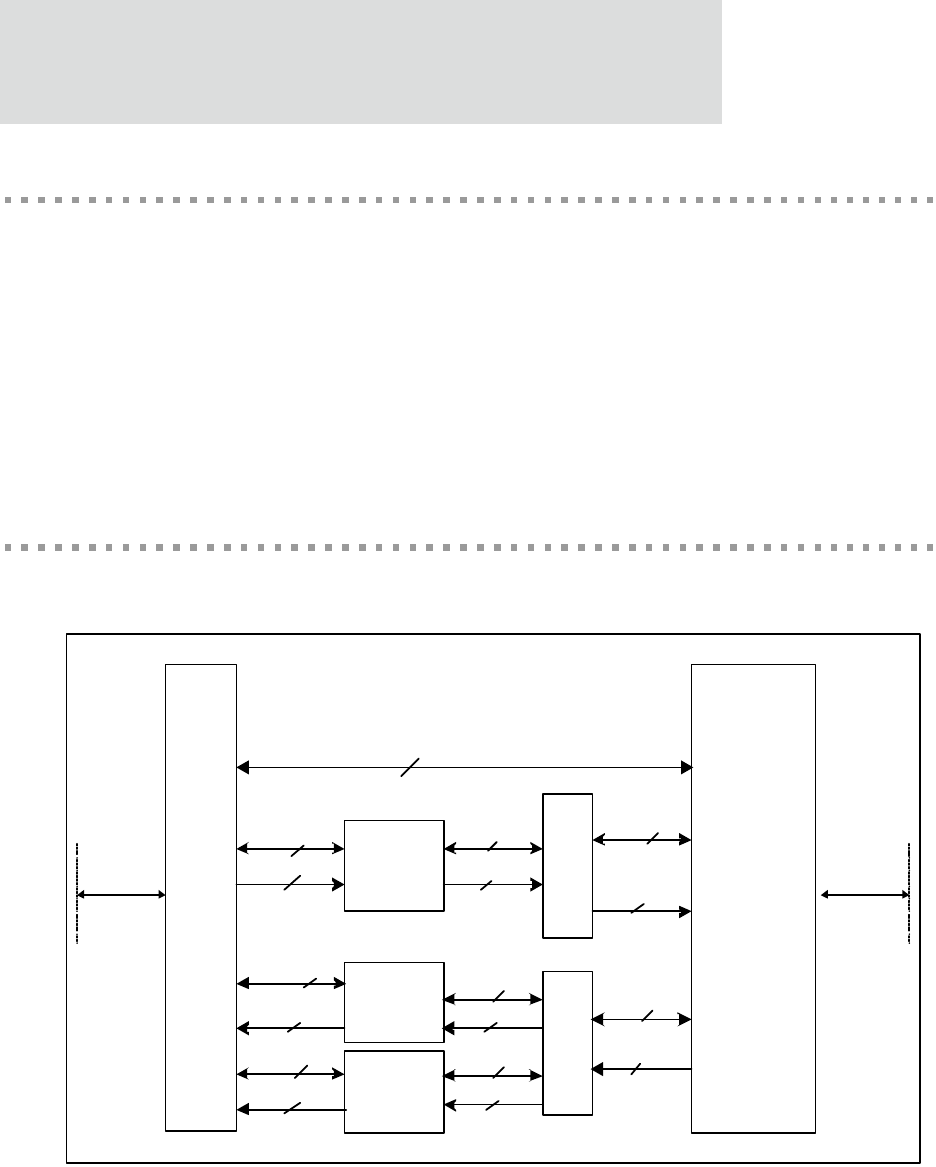

Figure 95 shows the block diagram of the IEEE 1284 peripheral port control module.

Figure 95: IEEE 1284 peripheral port control module

Reverse

FIFO

Forward

Data

FIFO

Forward

Command

FIFO

BBUS

Slave

and

DMA

Interface

R

E

V

F

W

D

Host Inte rf ace

BBus Interface IEEE 1284 Bus

IEEE 1284

Peripheral Port

Controller

Control

Control

Data

21

4

8

Control

2

Data 8

Control

Data

8

2

Control 4

Data 8

Control 2

Data 8

Control 2

Data

8

Control 2

Data

8

Data 8

Control 4