www.digiembedded.com

819

Timing

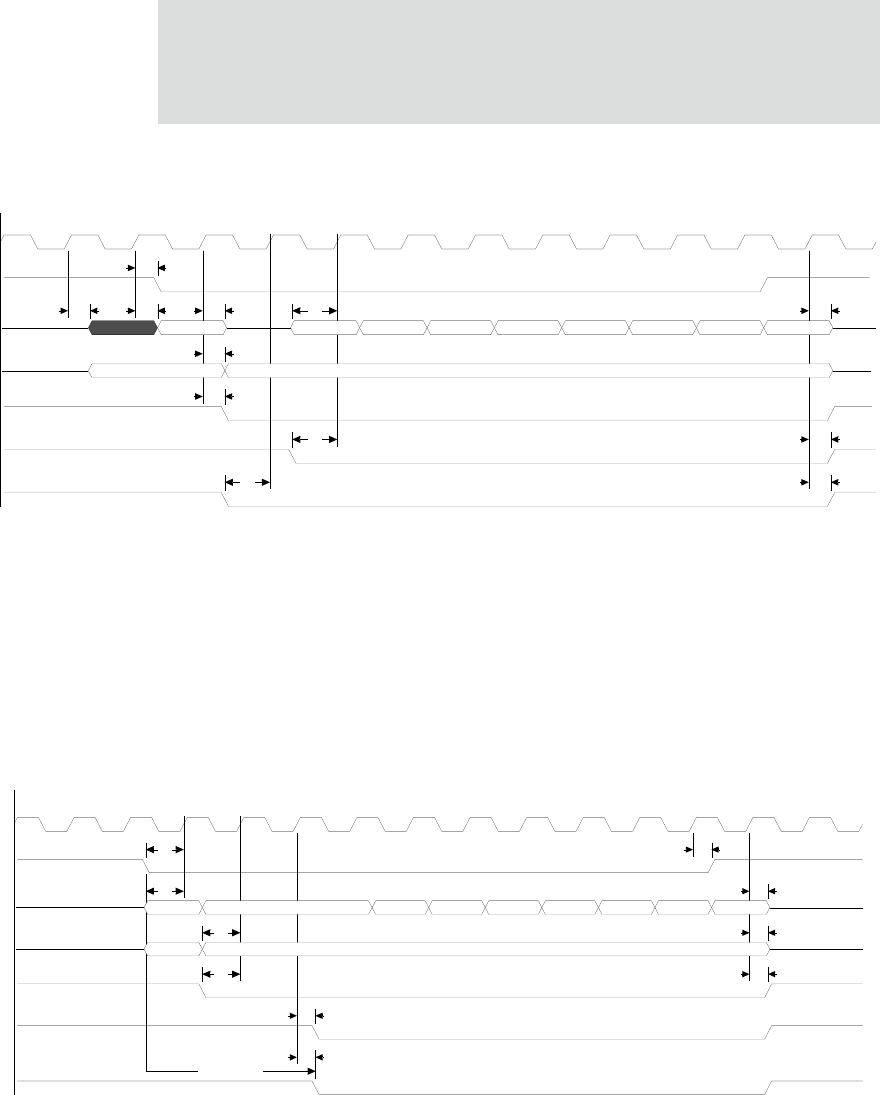

PCI burst read from NS9750 timing

Figure 123: PCI burst read from NS9750 timing

Note:

The functional timing for trdy_n, devsel_n, and the read data on ad[31:0] shows

the fastest possible response from the target.

PCI burst write to NS9750 timing

Figure 124: PCI burst write to NS9750 timing

P3P2

P3P2

P1

P1

P3P2P5P1P4

P1

byte enablescmd

addr data0 data1 data2 data3 data4 data5 data6 data7

pci_clk_in

frame_n

ad[31:0]

cbe_n[3:0]

irdy_n

trdy_n

devsel_n

3x pci_clk_in

P1

P1

P3P2

P3P2

P3P2

P3P2

byte enablescmd

addr data0 data1 data2 data3 data4 data5 data6 data7

pci_clk_in

frame_n

ad[31:0]

cbe_n[3:0]

irdy_n

trdy_n

devsel_n