System boot

10

NS9750 Hardware Reference

System boot

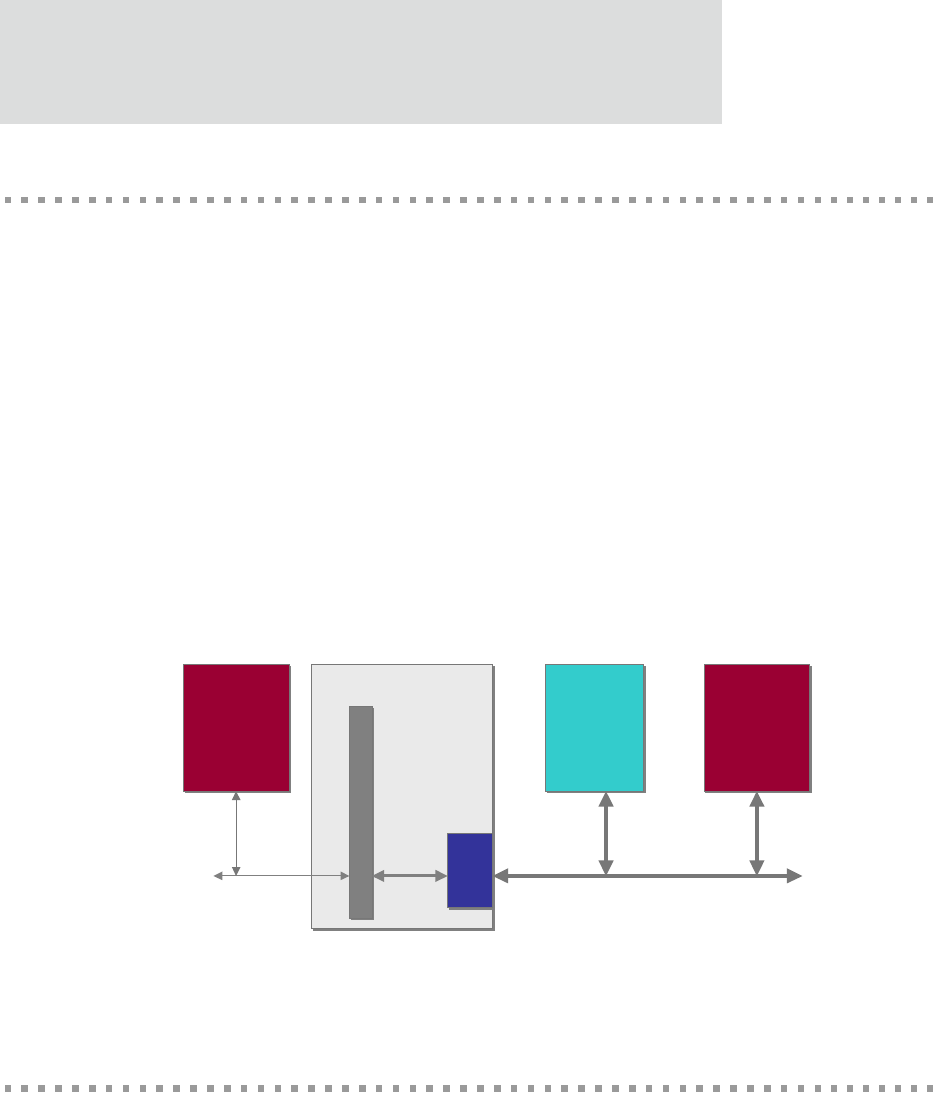

There are two ways to boot the NS9750 system (see Figure 2):

From a fast Flash over the system memory bus

From an inexpensive, but slower, serial EEPROM through SPI port B.

Both boot methods are glueless. The bootstrap pin,

RESET_DONE, indicates where to

boot on a system powerup. Flash boot can be done from 8-bit, 16-bit, or 32-bit ROM

or Flash.

Serial EEPROM boot is supported by NS9750 hardware. A configuration header in the

EEPROM specifies total number of words to be fetched from EEPROM, as well as a

system memory configuration and a memory controller configuration. The boot

engine configures the memory controller and system memory, fetches data from low-

cost serial EEPROM, and writes the data to external system memory, holding the CPU

in reset.

Figure 2: Two methods of booting NS9750 system

Reset

Master reset using an external reset pin resets NS9750. Only the AHB bus error status

registers retain their values; software read resets these error status registers. The

NS9750

Memory

CTL

External

System

Memory

Flash or

ROM

Memory Bus

Peripheral Bus to AHB Bus Bridge

AHB

Serial

EEPROM

SPI