www.digiembedded.com

351

Ethernet Communication Module

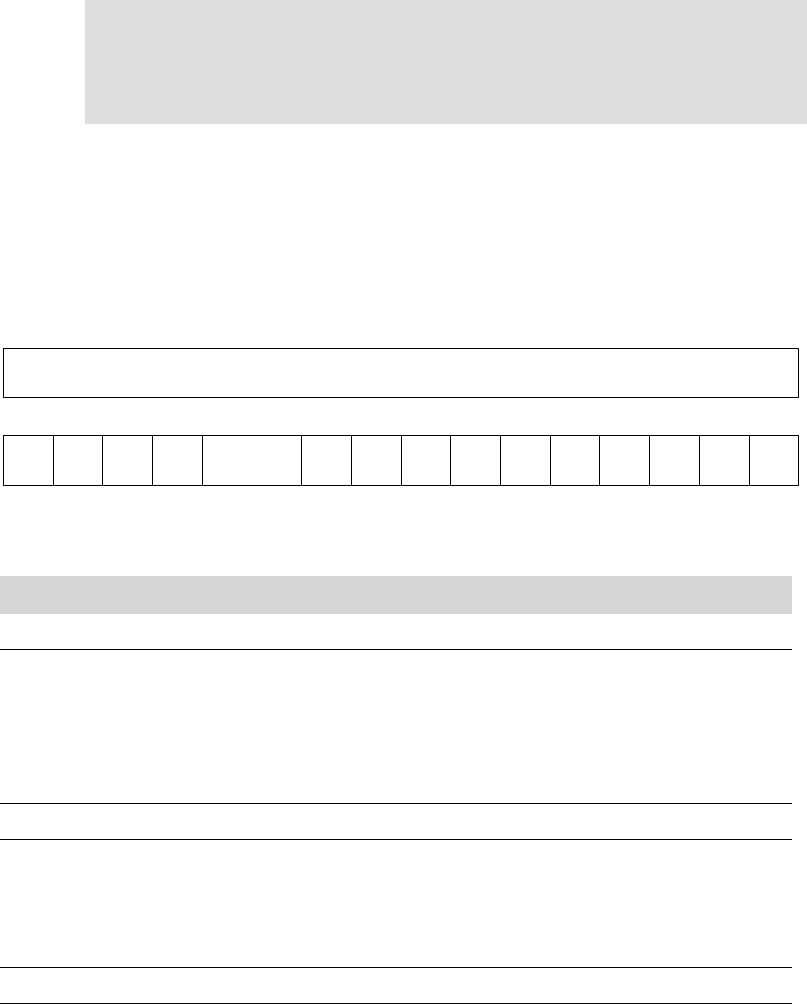

MAC Configuration Register #2

Address: A060 0404

MAC Configuration Register #2 provides additional bits that control functionality

within the Ethernet MAC block.

Register bit assignment

Bits Access Mnemonic Reset Definition

D31:15 N/A Reserved N/A N/A

D14 R/W EDEFER 0 Excess deferral

0 The MAC aborts when the excessive deferral limit is

reached (that is, 6071 nibble times in 100 Mbps mode

or 24,287 bit times in 10 Mbps mode).

1 Enables the MAC to defer to carrier indefinitely, as

per the 802.3u standard.

D13 R/W Not used 0 Always write to 0.

D12 R/W NOBO 0 No backoff

When this bit is set to 1, the MAC immediately retransmits

following a collision, rather than using the binary

exponential backoff algorithm (as specified in the 802.3u

standard).

D11:10 N/A Reserved N/A N/A

D09 R/W LONGP 0 Long preamble enforcement

0 Allows any length preamble (as defined in the 802.3u

standard).

1 The MAC allows only receive frames that contain

preamble fields less than 12 bytes in length.

Table 212: MAC Configuration Register #2

Reserved

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

ReservedRsvd

EDE

FER

LONGP PUREP CRCEN

Not

used

HUGE

Not

used

FULLD

Not

used

NOBO

AUTOP VLANP PADEN