www.digiembedded.com

427

PCI-to-AHB Bridge

Register bit assignment

Bits Access Mnemonic Reset Description

D31:10

Read only;

hard-wired to

0

Reserved N/A N/A

D09 R/W EN_BAR5 0 Enable bridge PCI Base Address register 5

0 Disable (default)

1 Enable

Note: Although

BAR_x can still be accessed

when

EN_BAR5 is 1, the address range

defined by

BAR_x will not be decoded.

D08 R/W EN_BAR4 0 Enable bridge PCI Base Address register 4

0 Disable (default)

1 Enable

Note: Although

BAR_x can still be accessed

when

EN_BAR4 is 1, the address range

defined by

BAR_x will not be decoded.

D07 R/W EN_BAR3 0 Enable bridge PCI Base Address register 3

0 Disable (default)

1 Enable

Note: Although

BAR_x can still be accessed

when

EN_BAR3 is 1, the address range

defined by

BAR_x will not be decoded.

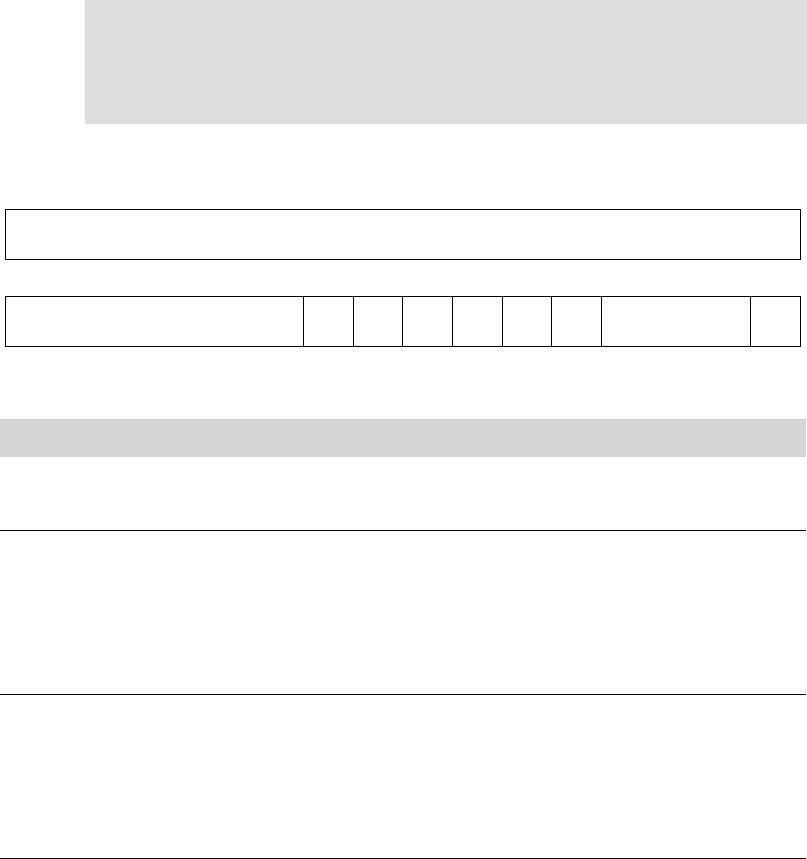

Table 263: PCI Miscellaneous Support register

Reserved

EN_

BAR1

EN_

BAR0

INTA2

PCI

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved Reserved

EN_

BAR5

EN_

BAR4

EN_

BAR3

EN_

BAR2