BBus Bridge Control and Status registers

498

NS9750 Hardware Reference

BBus Bridge Interrupt Status register

Address: A040 1000

This register contains the interrupt status of the BBus peripherals. All interrupts must

be serviced in the originating module.

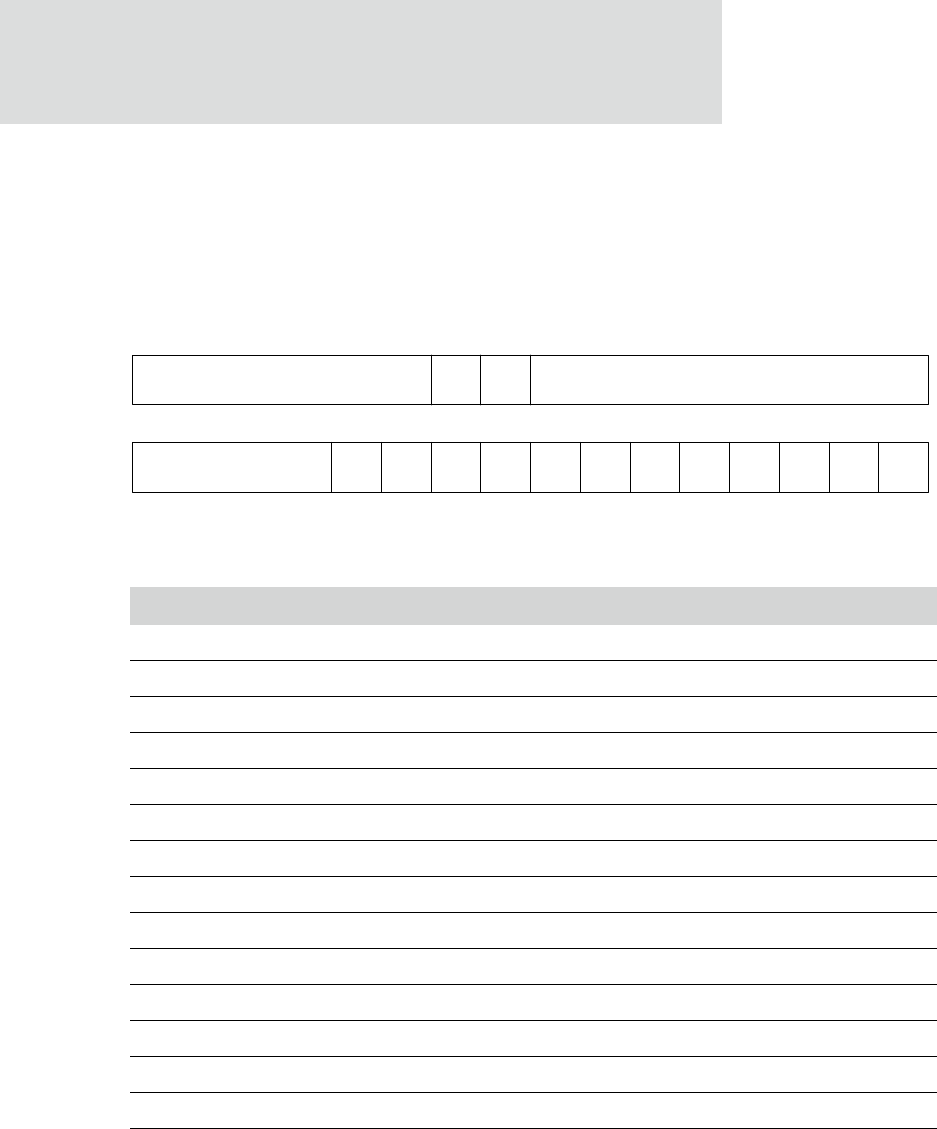

Register bit assignment

Bits Access Mnemonic Reset Description

D31:26 R Not used 00 Always set this field to 0.

D25 R ADMA2 0 AHB DMA channel #2 has asserted its interrupt.

D24 R ADMA1 0 AHB DMA channel #1 has asserted its interrupt.

D23:13 R Not used 0x000 Always set this field to 0.

D12 R Not used 0 Always write to 0.

D11 R 1284 0 IEEE-1284 module has asserted its interrupt.

D10 R I2C 0 I2C module has asserted its interrupt.

D09 R SDTX 0 SER transmit module D has asserted its interrupt.

D08 R SDRX 0 SER receive module D has asserted its interrupt.

D07 R SCTX 0 SER transmit module C has asserted its interrupt.

D06 R SCRX 0 SER receive module C has asserted its interrupt.

D05 R SATX 0 SER transmit module A has asserted its interrupt.

D04 R SARX 0 SER receive module A has asserted its interrupt.

D03 R SBTX 0 SER transmit module B has asserted its interrupt.

D02 R SBRX 0 SER receive module B has asserted its interrupt.

Table 300: BBus Bridge Interrupt Status register

Not used I2C1284 S4TX S4RX S3TX S3RX S2TX S2RX S1TX S1RX USB BBDMA

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

ADMA2 ADMA1 Not used

Not used