www.digiembedded.com

737

USB Controller Module

HcInterruptDisable register

Address: 9010 1014

Each disable bit in the HcInterruptDisable register corresponds to an associated

interrupt bit in the HcInterruptStatus register (see "HcInterruptStatus register,"

beginning on page 733). The HcInterruptDisable register works in conjunction with

the HcInterruptEnable register (see "HcInterruptEnable register," beginning on page

735). Writing a 1 in the HcInterruptDisable register clears the corresponding bit in the

HcInterruptEnable register; writing a 0 to a bit in the HcInterruptDisable register

leaves the corresponding bit in the HcInterruptEnable register unchanged.

On a read, the current value of the HcInterruptEnable register is returned.

D02 R/W SF 0b Start of frame

0 Ignore

1 Enable interrupt generation due to start of frame.

D01 R/W WDH 0b HcDoneHead writeback

0 Ignore

1 Enable interrupt generation due to HcDoneHead

writeback.

D00 R/W SO 0b Scheduling overrun

0 Ignore

1 Enable interrupt generation due to scheduling

overrun.

Bits Access Mnemonic Reset Description

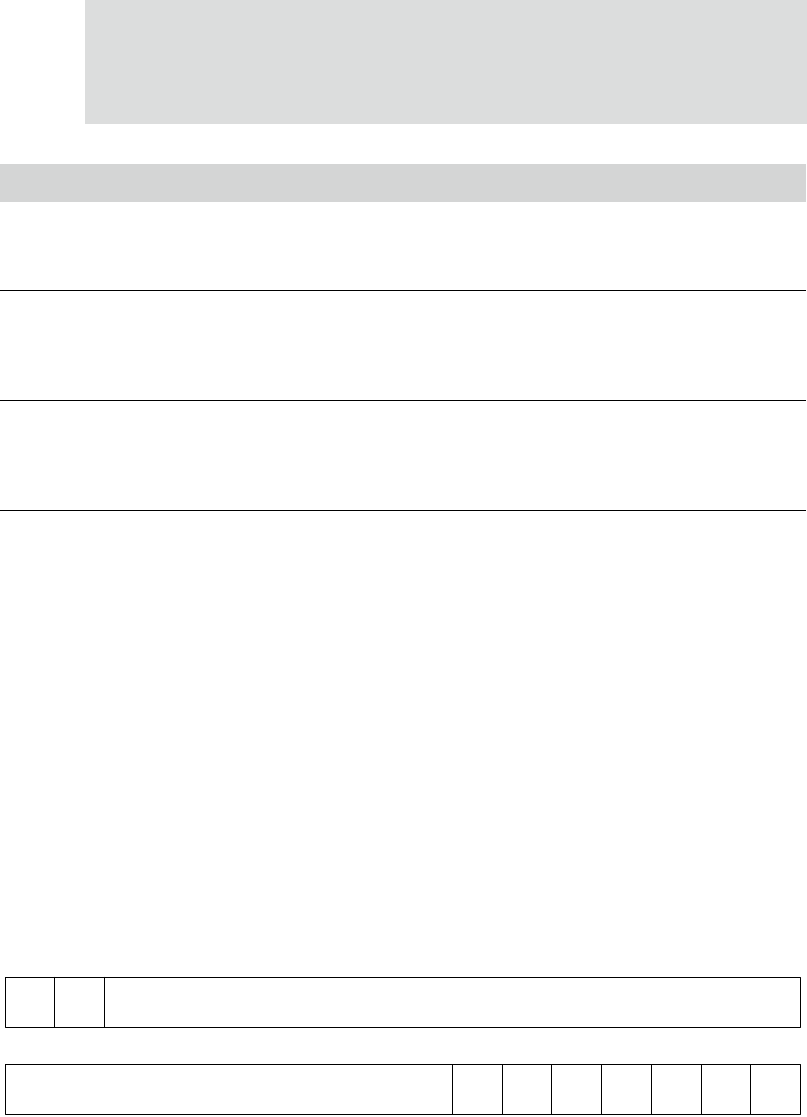

Table 427: HcInterruptEnable register

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

RD SF WDH SO

MIE OC Reserved

Reserved

RHSC FNO UE