Bridge control logic

470

NS9750 Hardware Reference

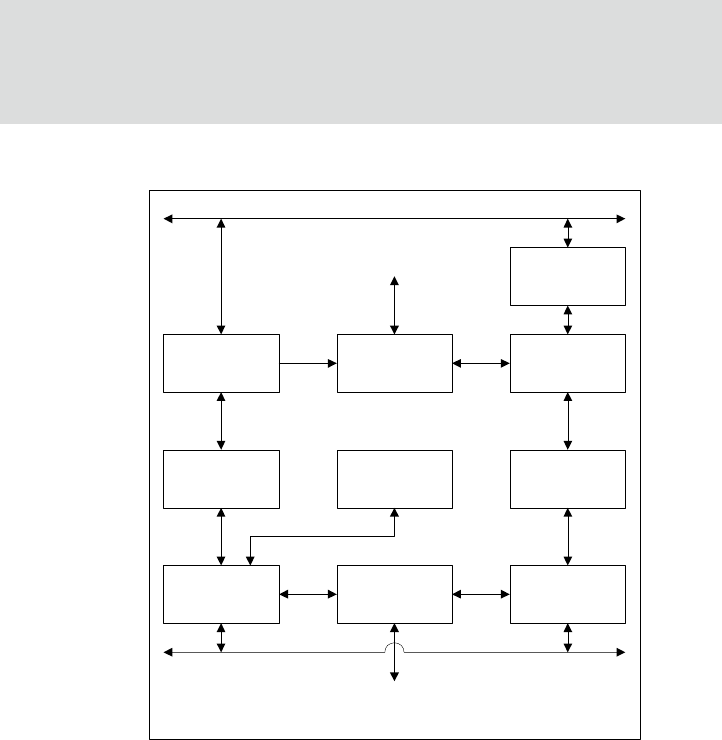

Figure 76: BBus bridge block diagram

Notes:

The AHB bus and BBus clock domains are asynchronous to each other.

A 4-entry bidirectional FIFO is implemented in the BBus-to-AHB data path to

allow burst transfers.

The FIFO size matches the maximum burst size supported by the BBus

masters.

The AHB-to-BBus data path does not support burst transfers, allowing only a

single entry bidirectional FIFO to be implemented in the data path. FIFO

size accommodates only one transaction at a time.

AHB Slave

BBUS Master

1 Entry

AHB

Retiming Fifo

BBUS Control

and Mux

BBUS Slave

4 Entry

BBUS

Retiming Fifo

AMBA AHB Bus

NetSilicon BBUS

BBUS arbitration with

other masters and slaves

User

Interface

AHB DMA

Controller

External DMA

Handshake

SPI-BOOT

Controller

AHB

Master