Overview

674

NS9750 Hardware Reference

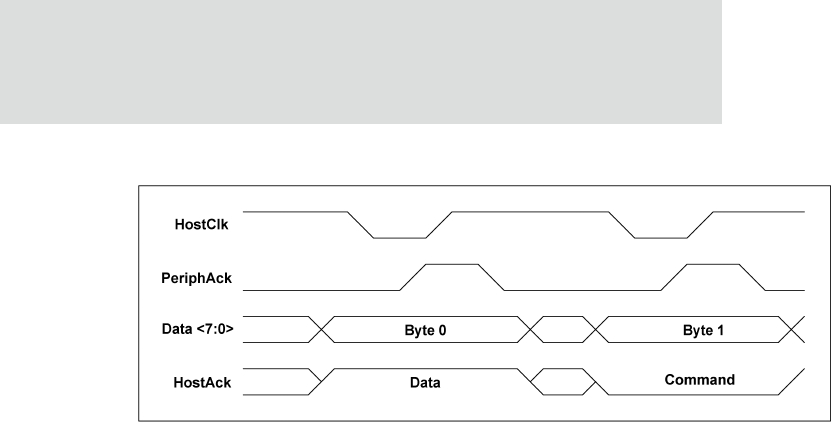

Figure 99: ECP mode forward transfer cycles

X Host processing sequence example:

1 The host puts the data on the data lines and indicates a data cycle by setting

HostAck high.

2 The host asserts HostClk low to indicate valid data.

3 The peripheral acknowledges the host by setting PeriphAck to high.

4 The host sets HostClk to high. This edge should be used to latch the data into the

peripheral.

5 The peripheral sets PeriphAck low, indicating that it’s ready for the next data byte.

6 The host sets HostAck to low to start the command transfer.

Note:

A forward transfer does not have to be a data transfer followed by a

command transfer. When

HostClk is low, the transfer will be data or

command depending on whether

HostAck is high or low.

Reverse transfer cycles

With the ECP protocol, changes in the data direction must be negotiated.

The host must request a reverse channel transfer by asserting the

ReverseRequest signal.

The host waits for the peripheral to acknowledge the request by asserting the

AckReverse signal. Only then can a reverse channel data transfer take place.

Figure 100 shows a reverse channel data cycle followed by a command cycle. In this

case,

PeriphClk is the data strobe and HostAck is the acknowledge signal.