Static memory controller

150

NS9750 Hardware Reference

partitioned memory devices" on page 150 and "Memory banks constructed from 8-bit

or non-byte-partitioned memory devices" on page 150 explain why different

connections, with respect to

WEOUT_n and BLSOUT[3:0]_n, for different memory

configurations.

Address connectivity

The static memory address output signal ADDROUT[27:0] must be right-justified.

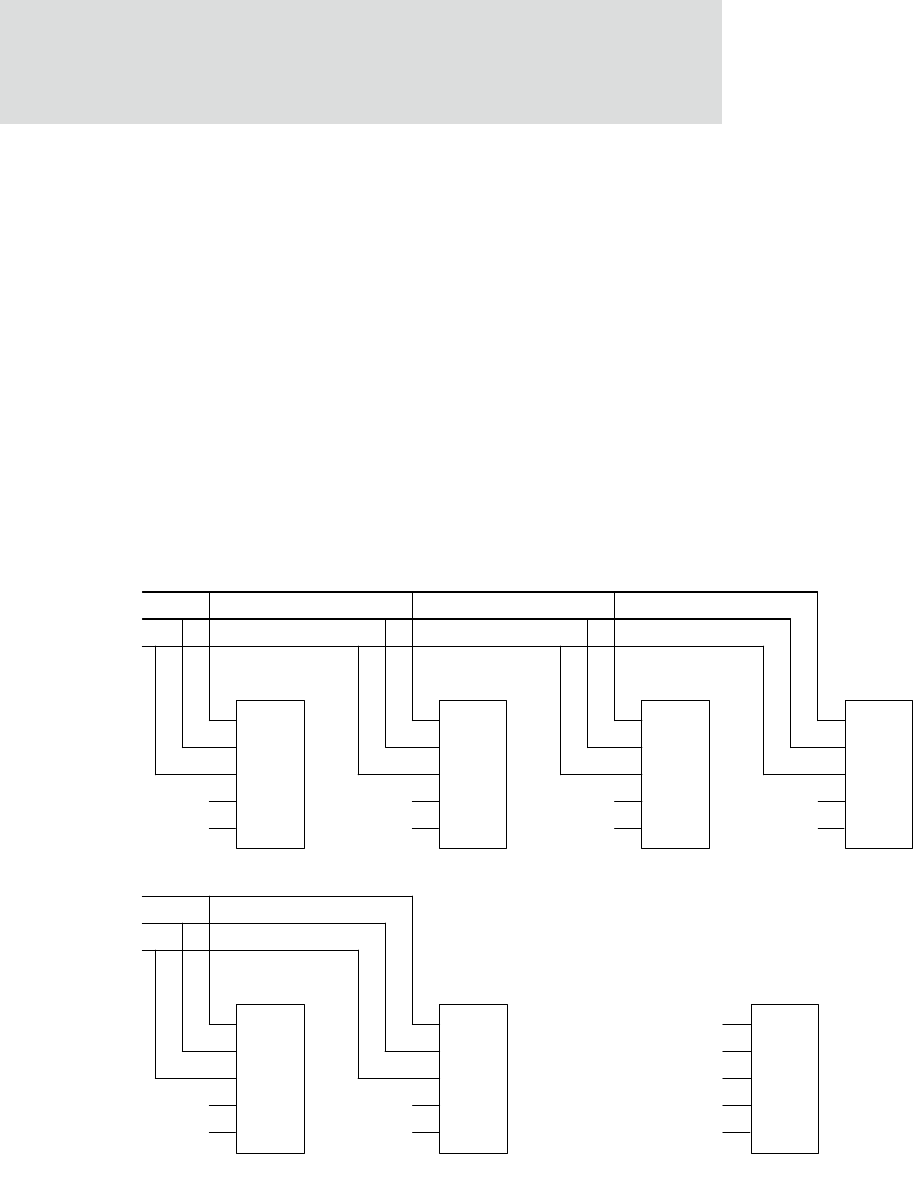

Memory banks constructed from 8-bit or non-byte-partitioned memory devices

For memory banks constructed from 8-bit or non-byte-partitioned memory devices, it

is important that the byte lane state (PB) bit is cleared to 0 within the respective

memory bank control register. This forces all

BLSOUT[3:0]_n lines high during a read

access, as the byte lane selects are connected to the device write enables.

A[20:0]

CE_n

OE_n

WE_n

IO[7:0]

BLSOUT[3]_n

DATA[31:24]

A[20:0]

CE_n

OE_n

WE_n

IO[7:0]

BLSOUT[2]_n

DATA[23:16]

A[20:0]

CE_n

OE_n

WE_n

IO[7:0]

BLSOUT[1]_n

DATA[15:8]

A[20:0]

CE_n

OE_n

WE_n

IO[7:0]

BLSOUT[0]_n

DATA[7:0]

32-bit bank consisting of four 8-bit devices

A[20:0]

CE_n

OE_n

WE_n

IO[7:0]

BLSOUT[1]_n

DATA[15:8]

A[20:0]

CE_n

OE_n

WE_n

IO[7:0]

BLSOUT[0]_n

DATA[7:0]

16-bit bank consisting of two 8-bit devices

A[20:0]

CE_n

OE_n

WE_n

IO[7:0]

BLSOUT[0]_n

DATA[7:0]

OEOUT_n

ADDROUT[20:0]_n

STCSOUT_n

8-bit bank consisting of one 8-bit device

ADDROUT[20:0]

STCSOUT_n

OEOUT_n

ADDROUT[20:0]

STCSOUT_n

OEOUT_n