www.digiembedded.com

829

Timing

6 C

load

= 10pf for all outputs.

7 SPI data order can be reversed such that LSB is first. Use the BITORDR bit in Serial Channel

B/A/C/D Control Register A.

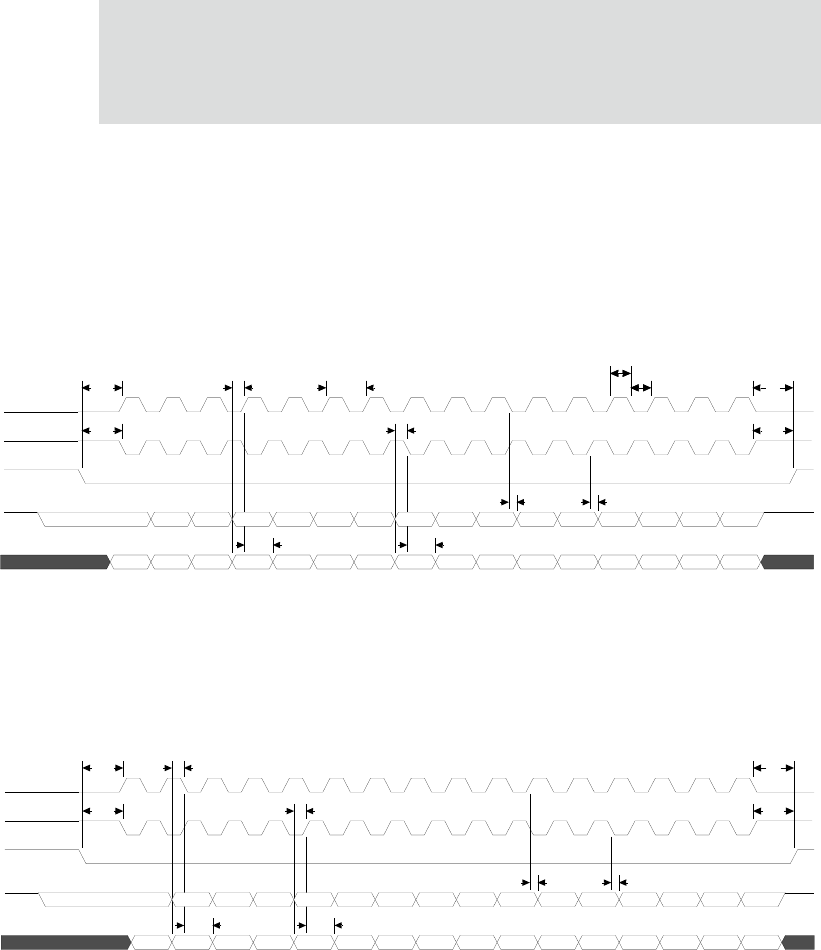

SPI master mode 0 and 1: 2-byte transfer

(see note 7)

Figure 136: SPI master mode 0 and 1 (2-byte transfer)

SPI master mode 2 and 3: 2-byte transfer

(see note 7)

Figure 137: SPI master mode 2 and 3 (2-byte transfer)

MSB LSB MSB LSB

MSB LSB MSB LSB

SP6SP4

SP8SP7

S10SP5SP1

S9SP12SP12

SP11SP11

SP13SP13SP3SP0

SPI CLK Out (Mode 0)

SPI CLK Out (Mode 1)

SPI Enable

SPI Data Out

SPI Data In

MSB LSB MSB LSB

MSB LSB MSB LSB

SP6SP4

SP8SP7

S10SP5SP1

S9SP3SP0

SPI CLK Out (Mode 2)

SPI CLK Out (Mode 3)

SPI Enable

SPI Data Out

SPI Data In