www.digiembedded.com

657

Serial Control Module: SPI

Serial Channel B/A/C/D Status Register A

Address: 9020 0008 / 0048

9030 0008 / 0048

The fields in Serial Channel B/A/C/D Status Register A operate differently when DMA

mode is used. Many fields are not required for DMA mode, as they are copied to the

status field in the DMA buffer descriptor. See the discussion of the DMA Buffer

Descriptor register status field in the BBus DMA Controller chapter.

Bits Access Mnemonic Reset Description

D31:26 N/A Reserved N/A N/A

D25:22 R Not used 0x0 This field is always read as 0x0.

D21:20 R RXFDB 00 Receive FIFO data available

00 Full word

01 One byte

10 Half word

11 Three bytes

This field is valid only when RRDY = 1.

Identifies the number of valid bytes contained in the next

long word to be read from the Serial Channel FIFO Data

register. The next read of the FIFO can contain one, two,

three, or four valid bytes of data. This field must be read

before the FIFO is read to determine which bytes of the 4-

byte long word contain valid data.

Normal endian byte ordering rules apply to the Serial

Channel FIFO Data register.

D19:16 R Not used 0 Always write as 0.

D15:13 N/A Reserved N/A N/A

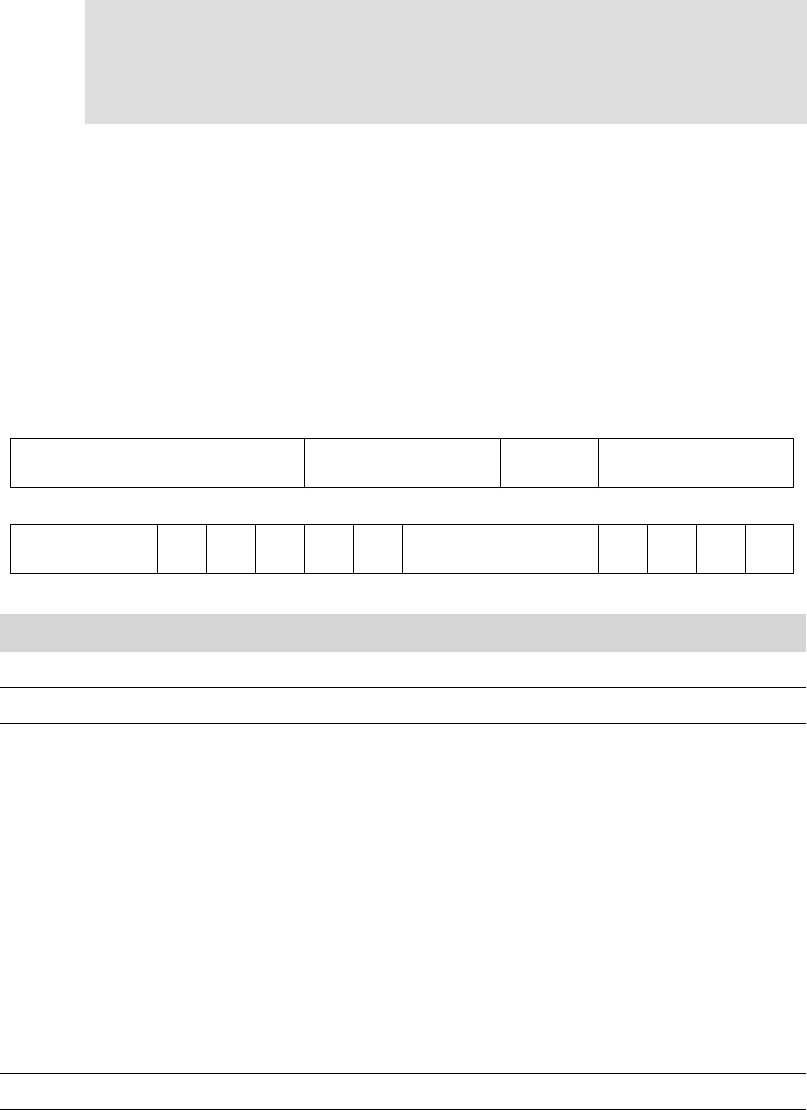

Table 386: Serial Channel B/A/C/D Status Register A

T

EMPTY

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

RXFDBNot used

THALFReserved ROVER RRDY RHALF RBC RFS TRDY Rsvd

Not used

Not used

Reserved