Reset

12

NS9750 Hardware Reference

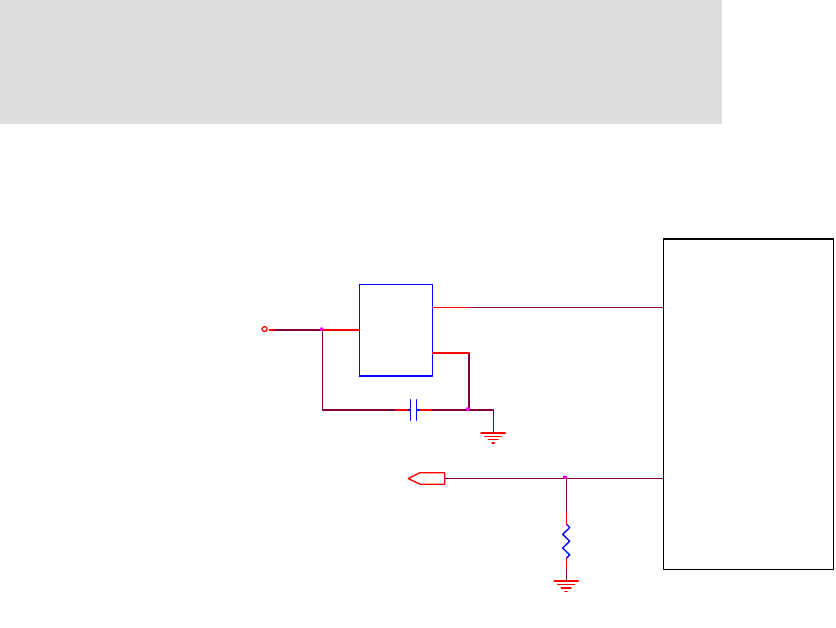

Figure 3 shows a sample reset circuit.

Figure 3: Sample reset circuit

You can use one of five software resets to reset the NS9750. Select the reset by

setting the appropriate bit in the appropriate register.

Watchdog timer can issue reset upon watchdog timer expiration (see

"Software Watchdog Timer register" on page 293).

AHB bus arbiter can issue reset upon AHB bus arbiter timer expiration.

AHB bus monitor can issue reset upon AHB bus monitor timer expiration.

Software reset can reset individual internal modules or all modules except

memory and CPU (see "Reset and Sleep Control register" on page 295).

The system is reset whenever software sets the PLL SW change bit to 1 (see

"PLL Configuration register" on page 299).

C14 100nF

Adding R5 will enable BOOT from Serial EE memory

connected to SPI port B to SDRAM located on dy_cs_n[0].

RESET_DONE remains “LOW” until BOOT is completed.

RESET_DONE = 1 indicates that the CPU is ready.

Otherwise, BOOT is from parallel ROM/FLASH connected to

st_cs_n[1].

RESET_

NS9750

RESET_DONE

RESETn

RESET delay required following valid

power applied to the NS9750 to allow

clock circuits to stabilize.

RST-

VCC

GND

U6

MAX809S_SOT23D

2

3

1

R5

2R4K

3R3V

RESET_DONE