www.digiembedded.com

61

Working with the CPU

R2: Translation Table Base register

Register R2 is the Translation Table Base register (TTBR), for the base address of the

first-level translation table.

Reading from R2 returns the pointer to the currently active first-level

translation table in bits [31:14] and an

UNPREDICTABLE value in bits [13:0].

Writing to R2 updates the pointer to the first-level translation table from

the value in bits[31:14] of the written value. Bits [13:0]

SHOULD BE ZERO.

Use these instructions to access the Translation Table Base register:

MRC p15, 0, Rd, c2, c0, 0 ; read TTBR

MCR p15, 0, Rd, c2, c0, 0 ; write TTBR

The CRm and opcode_2 fields SHOULD BE ZERO when writing to R2.

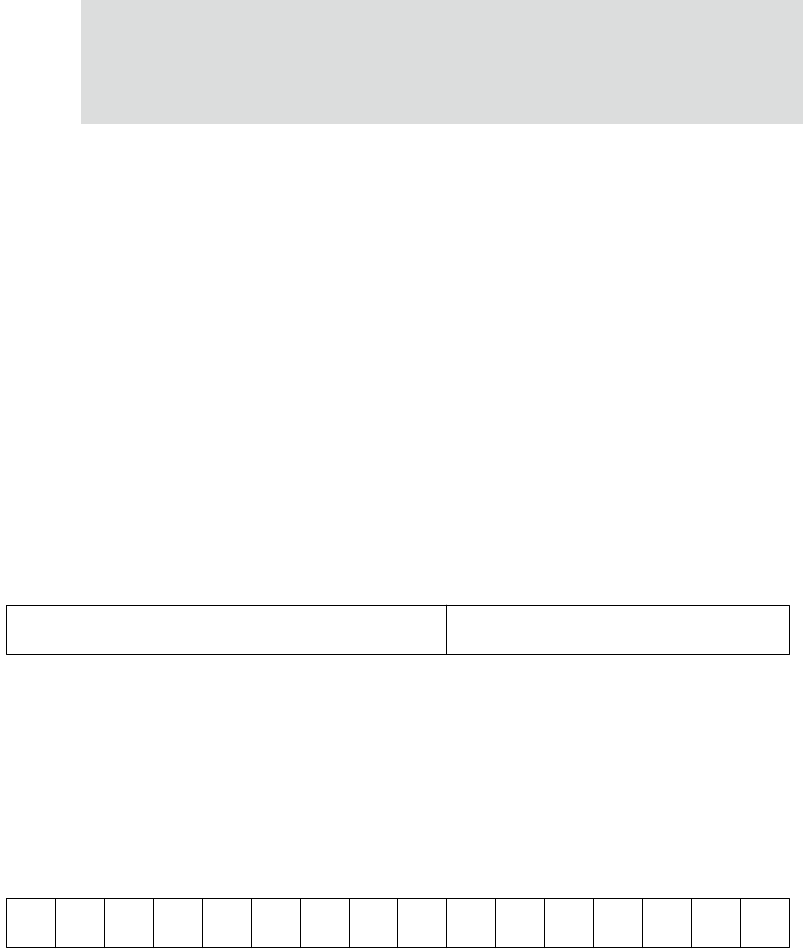

Figure 14 shows the format of the Translation Table Base register.

Figure 14: R2: Translation Table Base register

R3: Domain Access Control register

Register R3 is the Domain Access Control register and consists of 16 two-bit fields, as

shown in Figure 15.

Figure 15: R3: Domain Access Control register

Reading from R3 returns the value of the Domain Access Control register.

Writing to R3 writes the value of the Domain Access Control register.

31 014 13

Translation table base

UNP/SBZ

31 014 13 12 11 10 9 8 7 6 5 4 3 2 115161718192021222324252627282930

D0D1D2D3D4D5D6D7D8D9D10D11D12D13D14D15