www.digiembedded.com

87

Working with the CPU

Coarse page table descriptor

A coarse page table descriptor provides the base address of a page table that

contains second-level descriptors for either large page or small page accesses. Coarse

page tables have 256 entries, splitting the 1 MB that the table describes into 4 KB

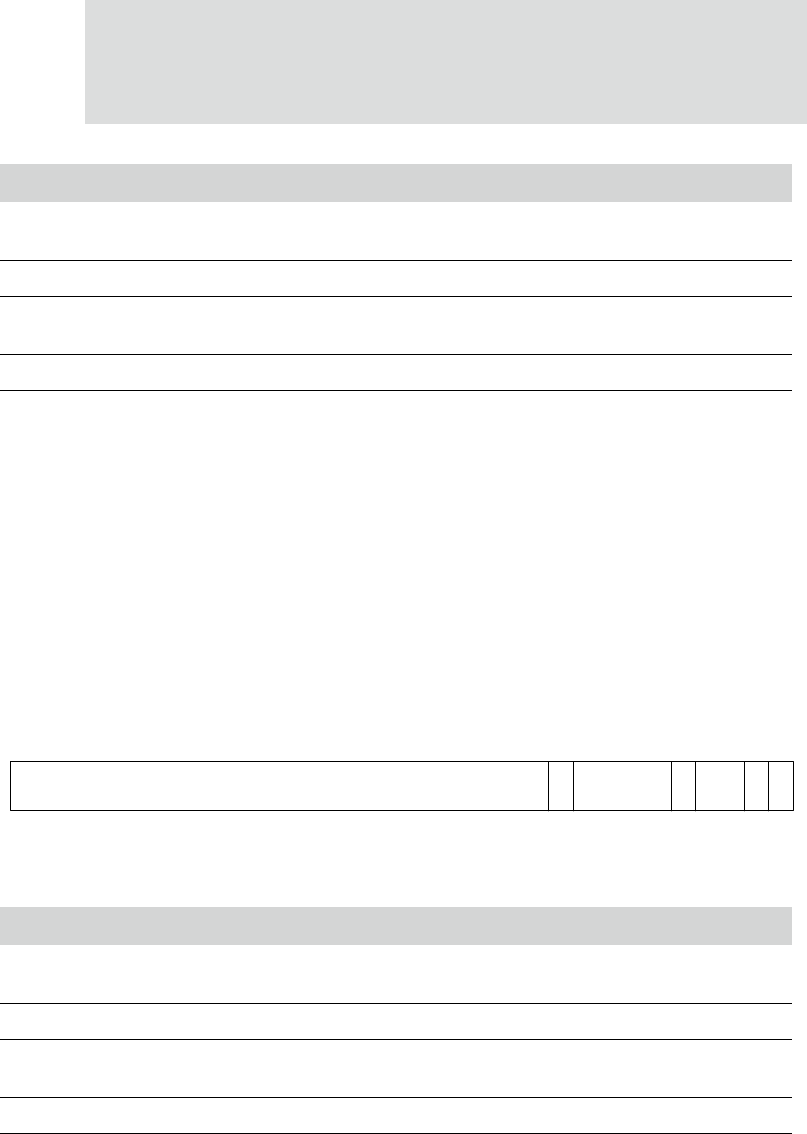

blocks. Figure 29 shows the coarse page table descriptor format; Table 35 describes

the coarse page table descriptor bit assignments.

Note:

If a coarse page table descriptor is returned from the first-level fetch, a

second-level fetch is initiated.

Figure 29: Coarse page table descriptor

[8:5] Specifies one of the 16 possible domains (held in the Domain and Access Control register)

that contain the primary access controls.

4 Should be written as 1, for backwards compatibility.

[3:2] Indicate if the area of memory mapped by this section is treated as writeback cachable,

write-through cachable, noncached buffered, or noncached nonbuffered.

[1:0] Must be 10 to indicate a section descriptor.

Bits Description

[31:10] Forms the base for referencing the second-level descriptor (the coarse page table index for

the entry derived from the MVA).

9 Always written as 0.

[8:5] Specifies one of the 16 possible domains (held in the Domain Access Control registers)

that contain the primary access controls.

4 Always written as 1.

[3:2] Always written as 0.

Table 35: Coarse page table descriptor bits

Bits Description

Table 34: Section descriptor bits

Coarse page table base address

S

B

Z

101

1023458931

SBZ

10

Domain