LCD controller functional overview

564

NS9750 Hardware Reference

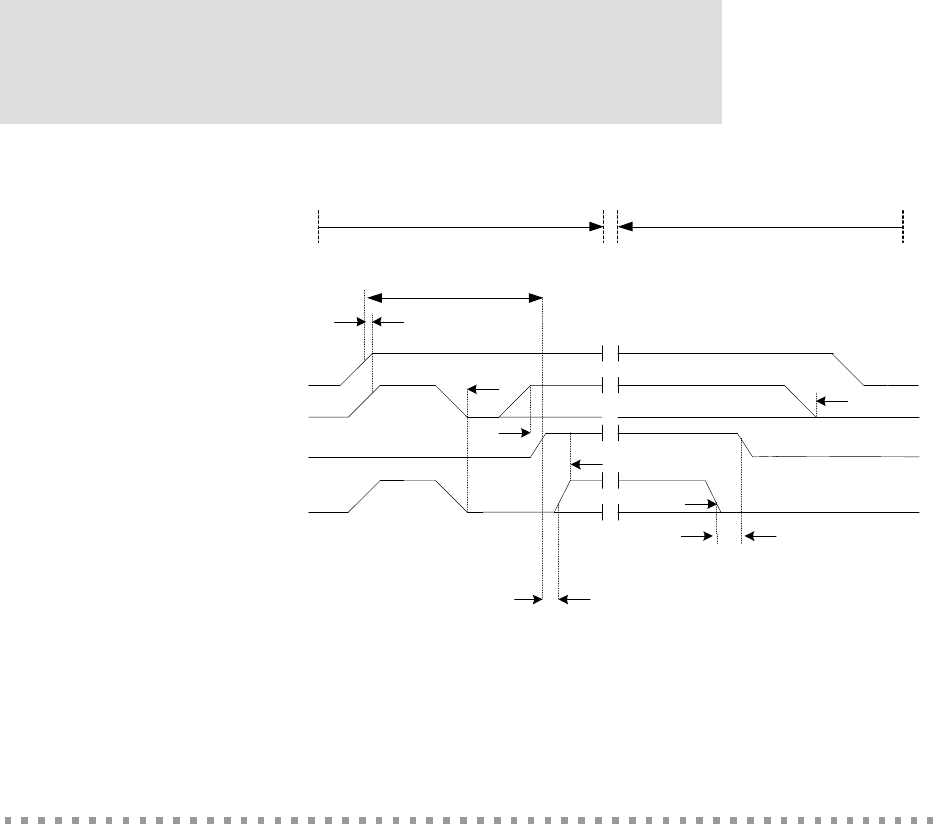

Figure 85: Power up and power down sequences

LCD controller functional overview

The LCD controller translates pixel-coded data into the required formats and timing

to drive a variety of single and dual mono and color LCDs.

The controller supports passive STN and active TFT LCD display types.

STN display panels require algorithmic pixel pattern generation to provide

pseudo-grayscaling on mono displays or color creation on color displays.

TFT display panels require the digital color value of each pixel to be applied

to the display data units.

Packets of pixel-coded data are fed, through the AHB interface, to two independent,

64-deep, 32-bit wide DMA FIFOs, which act as input data flow buffers. The buffered

pixel-coded data is then unpacked using a pixel serializer.

LCD on sequence LCD off sequence

Min. 0ms

Min. (display specific) ms

(provided through software)

Min. (display specific) ms

(provided through software)

Vdd

CLLP, CLCP, CLFP

CLAC, CLLE

Vee

CLPOWER

CLD[23:0]

Min. (display specific) ms

(provided through software)

LcdEn=1

LcdPwr=1

LcdEn=0

LcdPwr=0

LCD

Configured