Static memory controller

156

NS9750 Hardware Reference

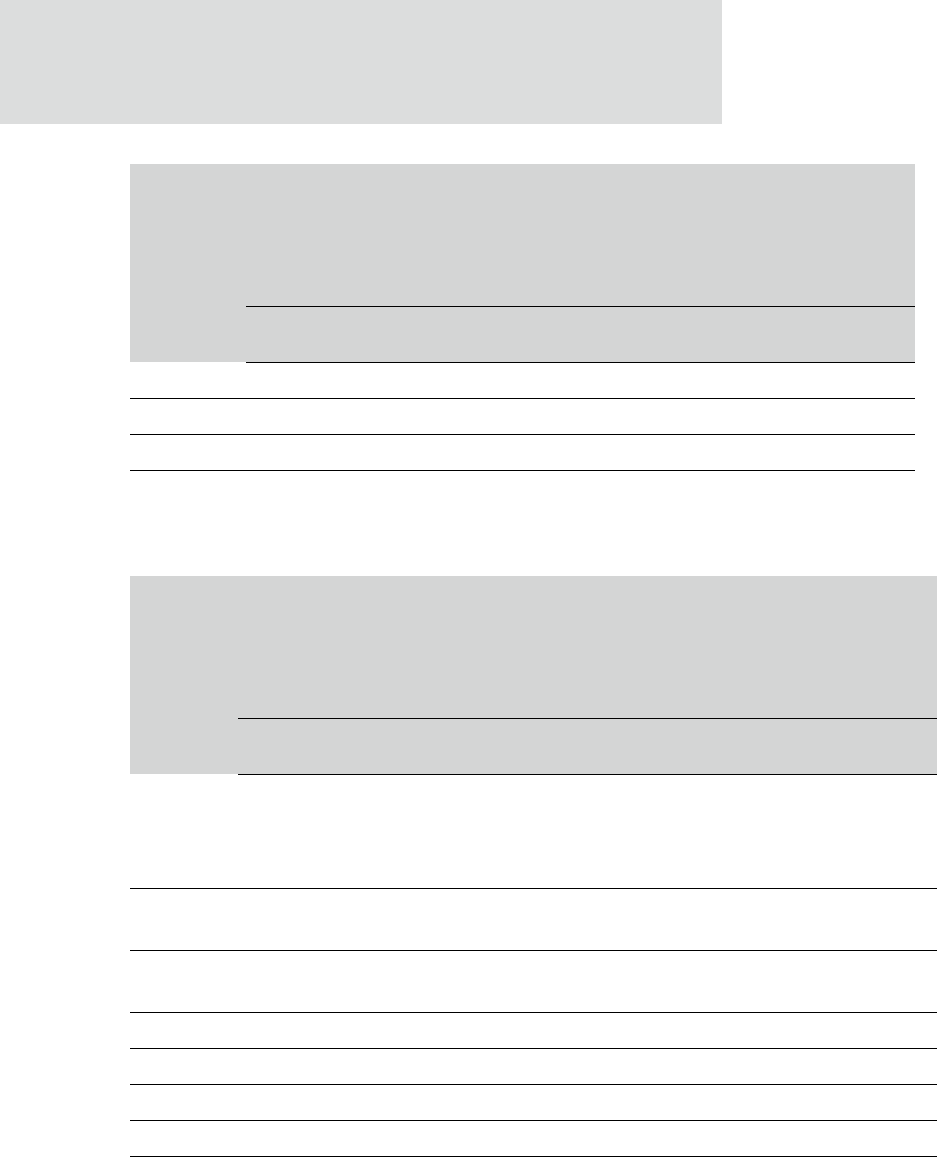

Byte 000 10 1011 - [23:16] - -

Byte 000 01 1101 - - [15:8] -

Byte 000 00 1110 ---[7:0]

Access: Write, little endian, 8-bit

external bus

System data mapping on to external

databus

Internal

transfer

width DATA to HRDATA

HSIZE

[2:0]

HADD

R [1:0]

ADDROUT

[1:0]

BLSOU

T [0]

[31:24] [23:16] [15:8] [7:0]

Word (4

transfers

010 -- 11

10

01

00

0

0

0

0

-

-

-

-

-

-

-

-

-

-

-

-

[31:24]

[23:16]

[15:8]

[7:0]

Halfword (2

transfers)

001 1- 11

10

0

0

-

-

-

-

-

-

[31:24]

[23:16]

Halfword (2

transfers)

001 0- 01

00

0

0

-

-

-

-

-

-

[15:8]

[7:0]

Byte 000 11 11 0 - - - [31:24]

Byte 000 10 10 0 - - - [23:16]

Byte 000 01 01 0 - - - [15:8]

Byte 000 00 00 0 - - - [7:0]

Table 82: Little endian write, 8-bit external bus

Access: Read, little endian, 32-bit

external bus

External data mapping on to system

databus

Internal

transfer

width

HRDATA to DATA

HSIZE

[2:0]

HADDR

[1:0]

BLSOUT

[3:0]

[31:24] [23:16] [15:8] [7:0]

Table 81: Little endian read, 32-bit external bus