USB Device Block registers

766

NS9750 Hardware Reference

Endpoint Descriptor #0–#11 registers

Address: 9010 2004 / 2008 / 200C / 2010 / 2014 / 2018 / 201C / 2020 / 2024 / 2028 / 202C / 2030

The Endpoint Descriptor registers store the endpoint information. There are 12

registers, one for each endpoint descriptor. Each register contains the same

information for the endpoint descriptor.

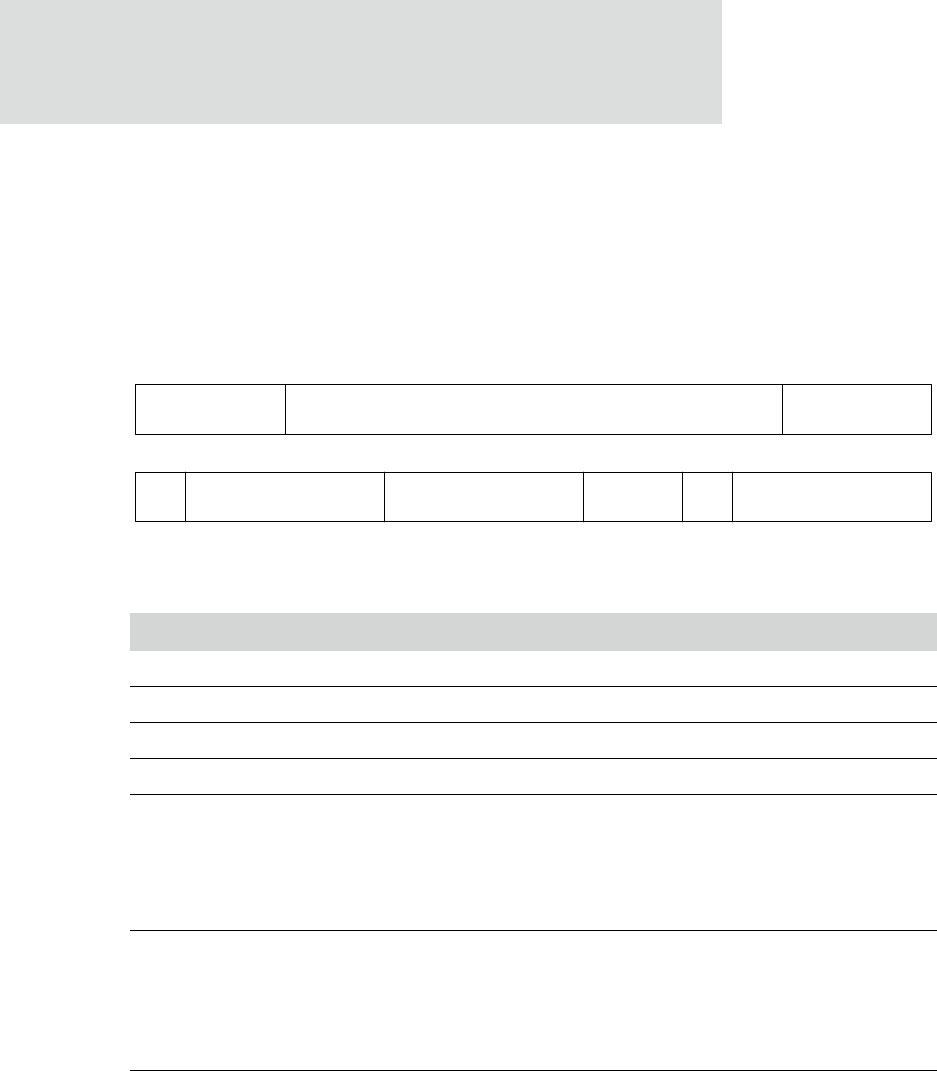

Register bit assignment

Bits Access Mnemonic Reset Description

D31:29 N/A Reserved N/A N/A

D28:19 R/W MPS 10’h0 Maximum packet size.

D18:15 R/W ALTSET 4’h0 Alternate setting to which this endpoint belongs.

D14:11 R/W INTN 4’h0 Interface number to which this endpoint belongs.

D10:07 R/W CNFGN 4’h0 Configuration number to which this endpoint belongs.

Note: Value at 0x0 is not supported if dynamic

programming is enabled (CSRPRG set to 1 in

the Device IP Programming Control and Status

register).

D06:05 R/W EDTP 2’h0 Endpoint type

00 Control

01 Isochronous

10 Bulk

11 Interrupt

D04 R/W EDDIR 1h’0 Endpoint direction

0Out

1In

Table 446: Endpoint Descriptor register (for endpoint descriptors 0–11)

13121110987654321015 14

31 29 28 27 26 25 24 23 22 21 20 19 18 17 1630

Reserved ALTSET

INTN

MPS

CNFGN EDDIR EDNBR

ALT

SET

EDTP