LCD timing

824

NS9750 Hardware Reference

5 These data widths are supported:

— 4-bit mono STN single panel

— 8-bit mono STN single panel

— 8-bit color STN single panel

— 4-bit mono STN dual panel (8 bits to LCD panel)

— 8-bit mono STN dual panel (16 bits to LCD panel)

— 8-bit color STN dual panel (16 bits to LCD panel)

— 24-bit TFT

— 18-bit TFT

6 See "LCDTiming0," beginning on page 580, and "LCDTiming1," beginning on page 582, for definitions of

the bit fields referred to in this table.

7 Note that data is sampled by the LCD panel on the falling edge of the CLCP in Figure 135, "LCD output

timing," on page 826). If the polarity of

CLCP is inverted, this parameter is relative to CLCP falling, instead.

8 C

load

= 10pf on all outputs.

9 CLCP high and low times specified as 50% of the clock period +/- 0.5ns.

10 Maximum allowable LCD panel clock frequency is 80 MHz.

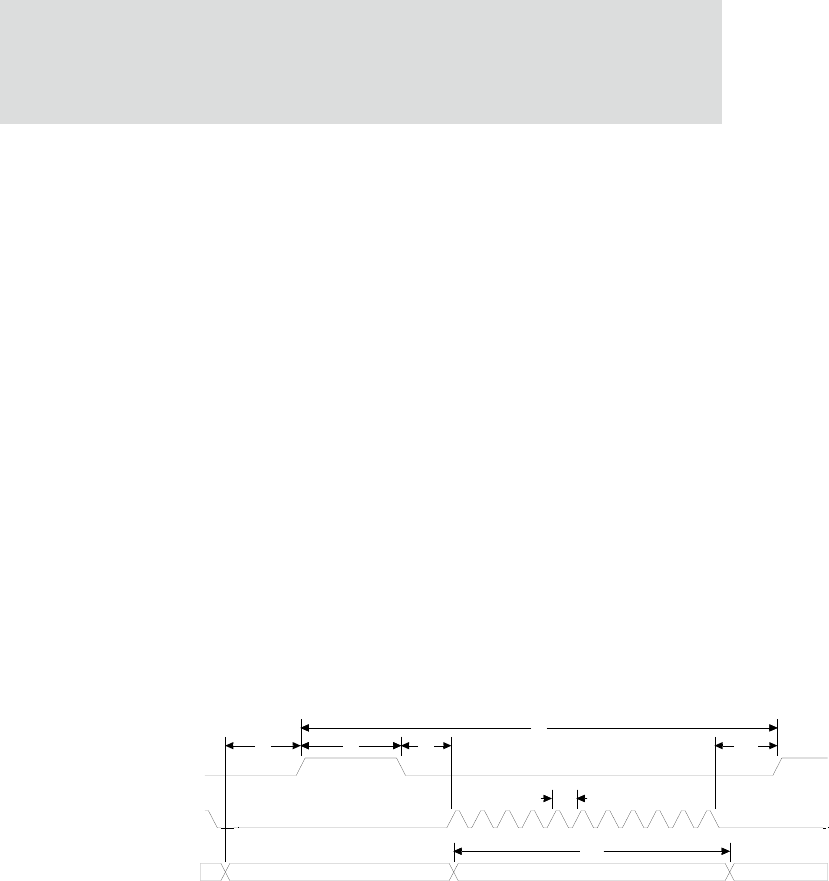

Horizontal timing for STN displays

Figure 129: Horizontal timing for STN displays

L15L15

L6L6

L17

L3

L4L2L1

L3

L2

Valid Display DataBlanking Blanking

CLLP

CLCP

CLD[7:0]